BEDO-DRAM

Die Abkürzung BEDO-DRAM, kurz für englisch Burst Extended Data Out DRAM, bezeichnet einen elektronischen Speicherbaustein. Dabei handelt es sich um eine spezielle Variante eines Extended Data Out DRAM (EDO-DRAM), d. h., ein dynamisches RAM (DRAM) bei denen die Ausgabedaten länger als normal anliegen und so einen schnelleren Zugriff auf die nächste Speicheradresse erlaubt.

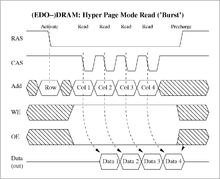

Im Unterschied zum EDO-DRAM wurde beim BEDO-DRAM die interne Steuerung dahingehend geändert, dass Daten in einem sogenannten Burst (dt. ungefähr Häufung) gelesen werden können, d. h., nach dem Anlegen einer Adresse kann die nachfolgende Speicheradressen einer Zeile in nur einem Taktzyklus gelesen werden. Dazu wird beim ersten Zugriff die Spalten- und Zeilenadresse wie beim normalen DRAM mit RAS (Row Address Strobe, Adressabtastimpuls für die Spalte) und CAS (Column Address Strobe, Adressabtastimpuls für die Spalte) angelegt. Für den Zugriff auf nachfolgende Speicherzellen der gleichen Zeile wird jedoch nur noch ein CAS-Signal genutzt. Dabei wird beim Aktivieren des CAS-Signals der interne Adresszähler erhöht, dies wird als Burst-Mode bezeichnet und erlaubt einen schnelleren Speicherzugriff auf aufeinander folgende Speicheradressen.

Da nur wenige Chipsätze unterstützt wurden, konnte sich diese Technik nicht am Markt durchsetzen.[1]

Quellen

[Bearbeiten | Quelltext bearbeiten]- Rolf Klaus, Hans Käser: Grundlagen der Computertechnik. vdf Hochschulverlag AG, 1998, ISBN 978-3-7281-2475-3, S. 85.

- Axel Sikora: Taschenbuch Digitaltechnik. Hanser Verlag, 2007, ISBN 978-3-446-40903-3, S. 320.

- Klaus Urbanski, Roland Woitowitz: Digitaltechnik: Ein Lehr- und Ubungsbuch. Springer, 2004, ISBN 978-3-540-40180-3, S. 230–231.

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Thomas Flik: Mikroprozessortechnik und Rechnerstrukturen. Springer, 2007, ISBN 978-3-540-26716-4, S. 695.