Register (Prozessor)

Register in Prozessoren sind Speicherbereiche für Daten, auf die Prozessoren besonders schnell zugreifen können.[1] Sie befinden sich direkt in der Nähe der Rechenwerke. In einem Prozessorkern stehen Register an der Spitze der Speicherhierarchie und sind daher die schnellste Möglichkeit Daten zu manipulieren, da der Speicherzugriff unabhängig vom Daten- oder Adress-Bus erfolgt.

Viele Prozessorarchitekturen, insbesondere Reduced Instruction Set Computer (RISC), erlauben Rechenwerken nur die Verarbeitung von Daten in Registern; andere Architekturen erlauben zumindest teilweise auch die Nutzung von Nicht-Registerinhalten aus dem Arbeitsspeicher oder aus Hardware-Registern.

Die Registersätze verschiedener Prozessorarchitekturen unterscheiden sich in der Größe, der Anzahl, und der Art der zur Verfügung stehenden Register:

- Einzelne Register haben heutzutage meist die Wortbreite einer Zweierpotenz, das heißt 8, 16, 32, 64, 128, 256 oder 512 bit.

- Die Anzahl an Registern pro Prozessorkern variiert von fünf bis mehrere hundert.

- Die unterschiedlichen Arten von Registern werden im Folgenden beschrieben.

Registertypen in einem Hauptprozessor-Kern

[Bearbeiten | Quelltext bearbeiten]Nach Charakteristik

[Bearbeiten | Quelltext bearbeiten]- Hardware-Register: physisch vorhanden, „namenlos“, vgl. physischer Adressraum

- Architektur-Register: sind für die Software „sichtbar“, vgl. logischer Adressraum.

Bei alten Hauptprozessoren (Zilog Z80, Intel i486) sind Hardware- und Architektur-Register identisch, bei moderneren Prozessoren (System/360 Model 91, Intel Pentium Pro, AMD K5, Intel Core) handelt es sich um unterschiedliche Dinge.

Nach Anzahl der enthaltenen Datenwerte

[Bearbeiten | Quelltext bearbeiten]- Skalare Register: enthalten einen einzelnen Datenwert, meistens Integer (Ganzzahlen), die auch als Speicheradressen verwendbar sind.

- Vektor-Register: Register, die mehrere Datenwerte (üblicherweise zwei bis 64) als Vektor enthalten. Die einzelnen Datenwerte können jeweils eine Größe von 8 bis 64 bit haben und Ganz- oder Gleitkommazahlen sein.

Nach Anwendungsfunktion

[Bearbeiten | Quelltext bearbeiten]Datenregister, Akkumulator

[Bearbeiten | Quelltext bearbeiten]Datenregister werden benutzt, um Operanden für die Arithmetisch-logische Einheit (arithmetic logic unit, ALU) und deren Resultate zu speichern. Bei älteren Prozessorarchitekturen gab es teilweise nur ein einziges solches Register, den Akkumulator; Prozessorkerne neuerer Generation besitzen oft mehrere Datenregister mit Akkumulatorfunktion.

In der Regel ist die Größe des Datenregisters zusammen mit der Breite des Datenbusses mit ausschlaggebend für die Einordnung einer Prozessorarchitektur als 8-, 16-, 32- oder 64-bit-Architektur. Mit 8-bit-Datenbus und 8-bit-Datenregistern wird sie als 8-bit-Architektur bezeichnet, z. B. MOS Technology 6502 oder Zilog Z80. Prozessoren mit unterschiedlicher Größe von Datenbus und Datenregistern werden häufig entsprechend bezeichnet, z. B. der Motorola 68000, der mit 16-bit-Datenbus und 32-bit-Datenregistern als 16-/32-bit-Prozessor bezeichnet wird. Die derzeit[Anmerkung 1] neuesten Prozessoren sind meistens 64-bit-Prozessoren, z. B. AMD Ryzen oder Intel Core i.

Bei 8-bit-Prozessoren waren Adressbus und -register meistens 16 bit groß. Bei den meisten heutigen Prozessoren sind die Adressregister genauso groß wie die Datenregister, der Adressbus meistens gleich groß oder kleiner.

Meistens sind die Datenregister nur mit der ALU verbunden, nicht jedoch mit der Gleitkommaeinheit (floating point unit, FPU). Das heißt, in den meisten Prozessorkernen können Datenregister nicht als Operanden für FPU-Operationen verwendet werden. In diesem Fall müssen Operanden für die FPU in speziell dafür vorgesehenen Registern gespeichert werden, den Gleitkommaregistern.

Frei verwendbare Register

[Bearbeiten | Quelltext bearbeiten]In modernen RISC-Prozessoren, so PowerPC oder SPARC, heißen die Datenregister allgemeine oder frei verwendbare Register (general purpose register, GPR), da sie sich als Daten- oder als Adressregister einsetzen lassen. Der Motorola 68000 verfügt in ähnlicher Weise über acht gleichwertige Datenregister.

Die 32-bit-Prozessoren der Intel-x86-Familie entstammen der Architektur Complex Instruction Set Computer (CISC) und besitzen daher weitgehend die Eigenschaften ihrer 8- und 16-bit-Vorgängergenerationen. So besitzen sie nur vier allgemeine Register, die auch noch mit den Namen aus jener Zeit bezeichnet werden (Akkumulator, Basisregister, Zählregister, Datenregister). Auch kann ein Prozessorkern nach wie vor gewisse Operationen nicht auf allen Registern durchführen (z. B. können Divisionen nur im Akkumulator stattfinden).

Adressregister

[Bearbeiten | Quelltext bearbeiten]Die Adressregister spielen eine wichtige Rolle in der Adressarithmetik. Sie werden genutzt, um Speicheradressen von Operanden oder Befehlen zu berechnen, und haben Verbindung mit dem internen Datenbus und dem Adressbus.

Bei indizierter Adressierung, beispielsweise beim Intel 8086, werden zwei Typen von Adressregistern unterschieden:

- die Basisadress-Register (auch „Segmentregister“), auf die unten bei den Spezialregistern eingegangen wird

- die Indexregister, welche den Offset zu einer Basisadresse speichern.

Bei linearer Adressierung, etwa beim Motorola 68000, gibt es keine solche Unterscheidung. Es gibt dort eine Adressierungsart, bei der ein Adress- und ein Datenregister addiert werden. Beim Motorola 68020 kann das Datenregister dabei zusätzlich mit einer fixen Wortbreite multipliziert werden.

Bei anderen Prozessorarchitekturen bezeichnet man als Indexregister auch das einzige an der Adressbildung beteiligte Register: beim Motorola 6800 und beim Zilog Z80 wird eine Konstante addiert, beim MOS Technology 6502 werden ein 16-bit-Wert und ein 8-bit-Indexregister addiert. Beim 6502 gibt es zusätzlich eine Adressierungsart, bei der eines von mehreren Basisadressregistern per Indexregister aus einer Tabelle ausgewählt werden kann, die im Arbeitsspeicher abgelegt ist. Die genaue Benennung der einzelnen Adressierungsarten ist uneinheitlich und prozessorspezifisch.

Spezialregister

[Bearbeiten | Quelltext bearbeiten]Neben allgemeinen Registern gibt es auch Spezialregister, die den Betriebszustand des Prozessorkerns speichern und Hilfsfunktionen für ihn erfüllen. Mit ihnen lassen sich nur Spezialoperationen ausführen (z. B. Division) oder sie haben ganz spezielle Funktionen (Interrupt descriptor table IDT, Seitentabelle …)

Spezialregister sind nur teilweise vom Anwender programmierbar.

Bei den meisten Architekturen sind folgende Spezialregister anzutreffen:

- Befehlszähler, auch Programmzähler (program counter, PC) oder Befehlszeiger (instruction pointer, IP (16 bit) bzw. extended instruction pointer, EIP (32 bit)): enthält je nach Systemarchitektur die Speicheradresse des derzeitigen oder des nächsten auszuführenden Befehls – eine Sprunganweisung setzt dieses Register auf einen neuen Wert

- Befehlsregister (instruction register): speichert den aktuellen Befehl – für den Programmierer nicht zugänglich

- Basisregister, z. B. für die Basisvektortabelle: kann von einem Benutzerprogramm neu gesetzt werden

- Segmentregister: eine Spezialität der x86-Plattform, welche die oberen 16 Bits einer 20-bit-Adresse enthält; ihr Inhalt muss also mit 16 multipliziert und dann zu einem segmentinternen Offset addiert werden, um die endgültige Speicheradresse zu erreichen (auf diese Weise konnten mit reinen 16-bit-Registerladebefehlen 20 bit Adressraum abgedeckt werden, also 1 MiB)

- Statusregister, auch Zustandsregister (condition code register, CCR) oder Programmstatuswort (program status word, PSW): gibt bestimmte Zustände nach Ausführung eines Befehls an (bspw. Zero-Flag, Vorzeichen-Flag etc.) – ein Benutzerprogramm initialisiert einzelne Flags z. B. vor arithmetischen Operationen

- Interrupt-Steuerregister (interrupt control register): Bei komplexeren Prozessoren, wo diese Funktionalität nicht mit einem oder zwei Bits im Statusregister (s. o.) abgehandelt werden kann, kann hierüber sehr differenziert vorgegeben werden, auf welche Interrupts überhaupt bzw. mit welcher Priorität reagiert werden soll. Durch Lesen kann die Software herausfinden, welcher der verschiedenen Interrupts überhaupt vorliegt. Durch Schreiben kann sie (temporär) z. B. einzelne Interrupts sperren, die während einer bestimmten Operation stören würden.

Der Refreshzähler des Zilog Z80, ein automatischer Zähler, der die Refresh-Adressen des Speichers generiert und von einigen Programmen als Pseudo-Zufallszahlengenerator verwendet wird, gehört ebenfalls in diese Kategorie.

Einige Mikrocontroller (Intel-MCS-51-Familie sowie Infineon-C167-Familie) organisieren diese Spezialregister und die Register zur Kontrolle der internen E/A-Ports in Form eines Registerspeichers, der sich mittels Memory Mapped I/O mit den gewöhnlichen Befehlen für den Arbeitsspeicherzugriff ansprechen lässt. Der durch diesen Registerspeicher verdeckte Arbeitsspeicher lässt sich entweder gar nicht oder nur indirekt ansprechen.

Stapelregister

[Bearbeiten | Quelltext bearbeiten]Die Stapelregister (auch Stapelzeiger oder Stackpointer, aus englisch stack pointer, kurz SP) sind Adressregister zur Verwaltung von Stapelspeichern, auch Kellerspeicher oder nur Stack genannt.

Ein Stapelspeicher wird von einem Stapelregister nach dem Last-In-First-Out-Prinzip organisiert und kann mit Push- oder Pop-Operationen gefüllt oder geleert werden. Dabei zeigt das Stapelregister immer auf die Speicheradresse am Ende des Stapelspeichers, je nach Architektur auf oder zumeist hinter das letzte Element.

Auf den meisten heutigen Architekturen existieren:

- ein System-Stack, den das Betriebssystem nutzt zur Sicherung und Restauration des Prozessorstatus bei der Prozessumschaltung.

- ein Anwender-Stack (Aufrufstapel), der von der Anwendungssoftware frei genutzt werden kann. Bei Aufruf eines Unterprogramms (Prozedur) wird zunächst die Rücksprungadresse auf dem Stack vermerkt, an der das aufrufende Programm fortgesetzt werden soll, wenn das Unterprogramm beendet ist. Zusätzlich kann dynamisch ein separater Stackbereich für die Aufruf-, Rückgabe- sowie lokalen Variablen des Unterprogramms angelegt werden, der nach Beendigung wieder freigegeben wird.

Nach elektrischer Typisierung

[Bearbeiten | Quelltext bearbeiten]

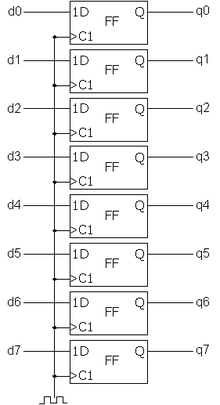

- einfache Latches, die einzelne Bits speichern können und sie zum Lesen ausgeben; das sind die meisten Register (Status-, Parallel-E/A-Datenregister).

- Mehrbit-Zählerregister, die darüber hinaus auf einen Impuls hin ihren Inhalt um 1 vergrößern oder verkleinern; Beispiele: der Programmzähler, das Stackregister und Timer-Register.

- Schieberegister kommen vor allem in der ALU eines Hauptprozessors oder einem numerischen Koprozessor vor, dort erfüllen sie u. a. Teilfunktionen bei Multiplikationen und Divisionen.

Eingabe-und-Ausgabe-Register

[Bearbeiten | Quelltext bearbeiten]Neben Puffer-Plätzen in der Zentraleinheit des Rechnersystems können Register auch in der Elektronik angeschlossener Peripheriegeräte oder -chips auftreten, aber auch der Hauptprozessor selbst kann über integrierte Eingabe-und-Ausgabe-Register verfügen. Sie lassen sich in der Regel in die gleichen Unterkategorien einteilen wie die o. g. reinen Hauptprozessor-Register. Ein paar repräsentative Beispiele:

- Die Statusregister der Steuerwerke der externen Massenspeicher umfassen neben Status- und Datenregistern in der Regel Adressregister, die sich auf Adressangaben des Massenspeichers beziehen, heute meistens Sektornummern.

- In Video-Chips steuern die Bits in den Statusregistern z. B. die verschiedenen Video-Modi; Datenregister können z. B. Sprite-Daten enthalten.

- Bei einer parallelen Schnittstelle enthält ein Datenregister die eigentlichen Druckdaten und ein Statusregister die Datenflusssteuerungs-Bits. Oft gibt es hier zusätzlich ein Statusregister namens DDR (für data direction register), über das die Datenrichtung (Ein- oder Ausgang) der Datenleitungen programmiert werden kann (z. B. bei bidirektionaler Verwendung).

Diese E/A-Register sind häufig über Portnummern als E/A-Ports auch vom Programm der Zentraleinheit erreichbar oder werden in den Adressraum des Hauptspeichers eingeblendet (Memory Mapped I/O). Je nach Sichtweise hat sich dabei dennoch die begriffliche Unterscheidung von Speicherplätzen in den RAM-Speicherbanken und Registerplätzen an Logikbausteinen erhalten.

Geschichte

[Bearbeiten | Quelltext bearbeiten]Bereits beim ersten Computer, dem Zuse Z3 von 1941, und seinem Vorgänger, dem Zuse Z1 von 1938, sind als Operanden für die arithmetischen Operationen im „Rechenwerk“ zwei Speicherstellen „R1“ und „R2“ in der Wortgröße der Maschine vorhanden. Zum Datenaustausch (Laden und Speichern) zwischen diesen Registern und dem vom Rechenwerk getrennt zu sehenden Speicherwerk sind spezielle Maschinenbefehle implementiert.

Die Entwicklung der Register ist also eng verknüpft mit der technischen Entwicklung des Arbeitsspeichers der frühesten Computer: Die ersten Computer hatten gar keinen Arbeitsspeicher im heutigen Sinne. Sämtliche Daten und das Programm selbst waren auf gänzlich anderen Medien, wie zum Beispiel mechanische Speicher, Lochkarten und magnetischen Trommelspeichern, abgelegt. Damit das Rechenwerk eine Operation ausführen konnte, mussten vom Massenspeicher Worte in die Pufferstellen des Rechenwerks übertragen werden, die einen Wert in die Schaltlogik abgeben konnten. Der am Ausgang der Schaltlogik entstehende Wert musste wieder gepuffert werden, bis er auf den Massenspeicher ausgeschrieben werden konnte. Ebendiese Pufferplätze nannte man Register (von lateinisch: regesta; aus regerere, „eintragen“).

Schon früh erkannte man, dass der Programmablauf optimiert werden konnte, wenn man Zwischenwerte auch über einige wenige Operationen hinweg puffern und etwa in der übernächsten Operation aufaddieren konnte. So wurden aus Einzelregistern ein Registersatz, der zuerst ebenfalls noch aus Elektronenröhren oder Relais bestand, mit fortschreitender technischer Entwicklung dann aber durch Kernspeicher ersetzt wurden. Die damit mögliche Adressberechnung für den Kernspeicher führte zu einer Aufspaltung der Begriffe – die Nennung als Register meint weiterhin Pufferplätze, deren Ort im Befehlscode des Rechenwerks hart codiert ist, während der Kernspeicher über Indexregister indirekt adressiert wird.

Zur Zeit der Kernspeicher waren die Datenwerte im Arbeitsspeicher noch direkt mit dem Rechenwerk verknüpft. Ein Befehlscode enthielt neben Rechenregistern, deren Wert direkt in die Rechenlogik einging, die codierte Angabe von Indexregistern, deren Wert auf die Adressleitungen des Kernspeichers gelegt wurde, und der ausgehende Wert der Ferritkerne dann in die Rechenlogik geführt wird. Der Kernspeicher konnte dabei einige tausend Plätze umfassen. Mit immer schnellerem Rechenwerk und dem Übergang zu billigerem, aber langsameren Hauptspeicher auf Basis von Kondensatoren (dynamischer RAM) wurden wieder Pufferplätze notwendig, bei dem Werte aus dem Hauptspeicher erst in Registerplätze am Rechenwerk kopiert werden, um von dort verarbeitet zu werden.

Benutzung in Programmiersprachen

[Bearbeiten | Quelltext bearbeiten]Einige höhere Programmiersprachen wie C sahen die explizite Benutzung von Registern für Variablen vor, die laut Vorstellungen des Programmierers besonders häufig benutzt werden. Moderne Compiler (seit Mitte der 1990er Jahre) ignorieren diese Attribute und überlassen die Zuweisung von Konstanten, Variablen oder Teilausdrücken dem Optimierer.[2] Mit der Programmiersprache C++ ist seit C++11 die Deklaration von „register“-Variablen mittels des gleichnamigen Schlüsselworts als veraltet erklärt, seit C++17 ist die Unterstützung gänzlich weggefallen.[3]

Anmerkungen

[Bearbeiten | Quelltext bearbeiten]- ↑ Stand: Januar 2024

Weblinks

[Bearbeiten | Quelltext bearbeiten]Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Claus Rautenstrauch, Thomas Schulze: Informatik für Wirtschaftswissenschaftler und Wirtschaftsinformatiker. Springer, Berlin 2003, ISBN 978-3-540-41155-0, 2.1.5 Prozessor, S. 26–31, doi:10.1007/978-3-642-56246-4.

- ↑ Dietmar Herrmann: Effektiv Programmieren in C und C++. 5. Auflage. Vieweg, Wiesbaden 2001, ISBN 978-3-528-44655-0, 8.2. Die Speicherklasse register, S. 145 f., doi:10.1007/978-3-322-94365-1.

- ↑ Remove Deprecated Use of the register Keyword. In: open-std.org. 21. Oktober 2015, abgerufen am 17. Juli 2024 (englisch).