Metall-Oxid-Halbleiter-Feldeffekttransistor

Ein Metall-Oxid-Halbleiter-Feldeffekttransistor (englisch metal-oxide-semiconductor field-effect transistor, MOSFET, auch MOS-FET, selten MOST) ist eine Bauform eines Transistors, d. h. eine Art elektronisches Ventil. In der Familie der Feldeffekttransistoren zeichnen sich MOSFETs durch ein isoliertes Gate (der Kontakt, mit dem das „Ventil“ angesteuert wird) aus einem Oxid aus und gehören damit zu den Feldeffekttransistoren mit isoliertem Gate (IGFET) bzw. Metall-Isolator-Halbleiter-Feldeffekttransistoren (MISFET).

MOSFETs basieren auf einer Metall-Isolator-Halbleiter-Struktur, d. h. einem schichtweisen Aufbau aus einer isolierten metallischen Gate-Elektrode, einem Halbleiter und dem dazwischen befindlichen oxidischen Dielektrikum (also einem Isolierstoff). In modernen integrierten Schaltungen wurde im Laufe der technischen Entwicklung das metallische Gate durch hochdotiertes Polysilizium mit metallähnlichen elektrischen Eigenschaften ersetzt. Trotz des abweichenden Aufbaus wurde auch für diese Variante die Bezeichnung MOSFET weitgehend beibehalten, siehe auch Abschnitt Name.

Wie bei allen Feldeffekttransistoren erfolgt die Steuerung des Stromflusses im Halbleiterbereich zwischen den beiden elektrischen Anschlüssen Drain und Source über eine elektrische Steuerspannung (Gate-Source-Spannung) bzw. Steuerpotential (Gate-Potential), vgl. Abschnitt Aufbau und Funktionsweise. Daher sind MOSFETs spannungsgesteuerte aktive elektrische Bauelemente und funktionieren grundlegend anders als bipolare Transistoren, einer anderen bedeutenden Gruppe von Transistoren, die stromgesteuert arbeiten, d. h., umso mehr elektrischen Strom durchlassen, je mehr Strom in die Steuerelektrode fließt.

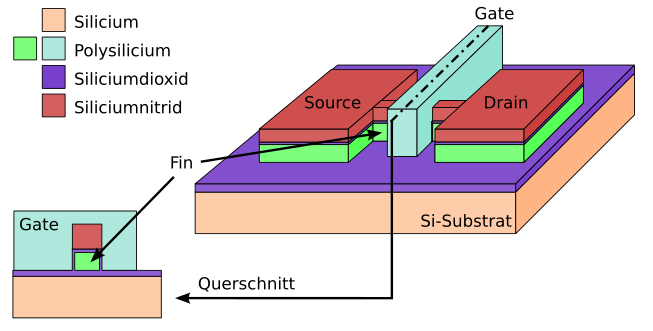

Aufgrund fertigungstechnischer Vorteile ggü. anderen Varianten sind MOSFETs mit Silizium als Halbleitermaterial seit den 1970er Jahren zum meistverwendeten Transistortyp für analoge und digitale integrierte Schaltungen geworden. Hier kommen sie unter anderem als Teil von Logik-Gattern in digitalen Schaltungen zum Einsatz. Die Entwicklung in diesem Bereich ist für die stetige Skalierung der Transistoren bekannt. Hier konnten die Packungsdichte für diese Art von Transistoren um Größenordnungen erhöht und durch Massenfertigung die Herstellungskosten gering gehalten werden, so dass beispielsweise im Jahr 2008 in einem einzelnen Prozessor bis zu 1,9 Milliarden Transistoren verbaut wurden. Durch Nutzung neuer Varianten, wie den FinFETs, konnte die Skalierung weiter fortgesetzt werden. So ist es in 7-nm-Technik möglich, über 54 Milliarden Transistoren in einem Prozessor (Nvidia GA100 Ampere) zu verbauen.[1]

Auch bei anderen Anwendungen, wie Schalten von hohen Strömen oder mit hohen Spannungen (vgl. Leistungstransistor) sind Silizium-MOSFETs in vielen Bereichen vertreten oder gar Standard, andere Materialien sind Galliumarsenid oder auch organische Halbleiter. Zunehmend werden jedoch die physikalischen Grenzen von Silizium ausgereizt, und für besondere Anwendungen sind heute andere Halbleitermaterialien mit für diese Anwendung besseren Eigenschaften als Silizium interessant, wie Verbindungshalbleiter oder Halbleiter mit größeren Bandlücken, wie Siliziumcarbid (SiC) und Galliumnitrid (GaN), auch wenn die Fertigungskosten derzeit noch beträchtlich höher liegen.

Geschichte

[Bearbeiten | Quelltext bearbeiten]

Das Funktionsprinzip von MOSFETs ist etwa 20 Jahre älter als das des Bipolartransistors. Die ersten Patentanmeldungen stammen aus den Jahren 1926 von Julius Edgar Lilienfeld[2] und 1934 von Oskar Heil. Die ersten MOSFETs wurden allerdings erst 1960 von Mohamed M. Atalla und Dawon Kahng in den Bell Labs gefertigt, die mit dem Materialsystem Silizium/Siliziumdioxid einen Fertigungsprozess entwickelten, mit dem sich eine reproduzierbar gute Halbleiter-Isolator-Grenzfläche herstellen ließ.[3] Damit verbunden war die Abkehr vom Germanium als Basismaterial und steigende Anforderungen an die Fertigungsbedingungen (Reinräume, strenges Temperaturregime).

Ab Anfang bzw. Mitte 1970 kam dotiertes Polysilizium als Gate-Material zum Einsatz und verdrängte damit aufgedampftes Aluminium.[4] Seit der Jahrtausendwende wurde verstärkt an der neuartigen High-k+Metal-Gate-Technik geforscht und diese 2007 erstmals in der Massenproduktion eingesetzt.

Name

[Bearbeiten | Quelltext bearbeiten]Der Name Metall-Oxid-Halbleiter-Feldeffekttransistor geht auf die ursprüngliche Schichtfolge des Gate-Schichtstapels zurück. Bis Anfang der 1980er-Jahre dominierte die Verwendung von Aluminium (ein Metall) als Gate-Material, das durch eine nichtleitende Siliziumdioxidschicht (Isolator) vom leitfähigen Kanal im Siliziumsubstrat (Halbleiter) getrennt war. In den 1980er-Jahren verbreiteten sich zunehmend Prozesse, die dotiertes Polysilizium als Gate-Material nutzten. Dies ist bis heute die häufigste Bauform handelsüblicher CMOS-Schaltkreise. Da kein Metall verwendet wird, ist die Bezeichnung MOSFET nicht mehr korrekt, wird aber weiterhin als Synonym genutzt.

Mit zunehmender Miniaturisierung zeigen MOS-Transistoren mit Polysilizium-Gate elektrische Nachteile, denn bei bestimmten Beschaltungen bildet sich ein Verarmungsbereich im Gate aus (Polysiliziumverarmung). Daher wurde seit Anfang der 2000er-Jahre nach alternativen Gate-Materialien (z. B. Übergangsmetalle) geforscht. Parallel dazu wurde auch nach alternativen Isolatormaterialien mit hoher Dielektrizitätskonstante (sogenannte High-k-Materialien) geforscht, um die steigenden Leckströme zu reduzieren. 2007 führte Intel als erster Hersteller die Kombination beider Änderungen (vgl. High-k+Metal-Gate-Technik) ein; einige weitere Hersteller von Hochleistungsprozessoren folgten. In diesen Fällen ist die Bezeichnung MOSFET daher wieder korrekt, dennoch ist es oft günstiger, die neutrale Bezeichnung MISFET (Metall-Nichtleiter-Halbleiter-FET) oder ganz allgemein IGFET (FET mit isoliertem Gate) zu verwenden.

Aufbau und Funktionsweise

[Bearbeiten | Quelltext bearbeiten]

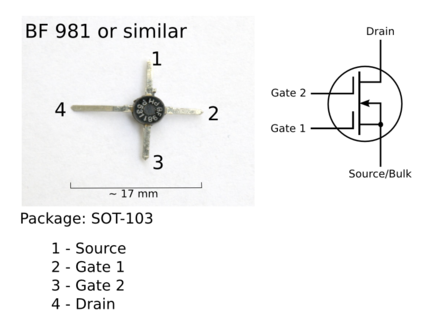

Ein MOSFET ist ein aktives Bauelement mit mindestens drei Anschlüssen (Elektroden): G (gate, dt. Steuerelektrode), D (drain, dt. Abfluss), S (source, dt. Quelle). Bei einigen Bauformen wird ein zusätzlicher Anschluss B (bulk, Substrat) nach außen geführt, der mit der Chiprückseite verbunden ist. Da eine Spannung an der Chiprückseite zusätzliche elektrische Felder erzeugt, die auf den Kanal wirken, verschiebt sich, wenn man die Spannung am B-Anschluss ändert, die Threshold-Spannung des MOSFETs. Meistens ist das Substrat jedoch intern mit dem Source verbunden.

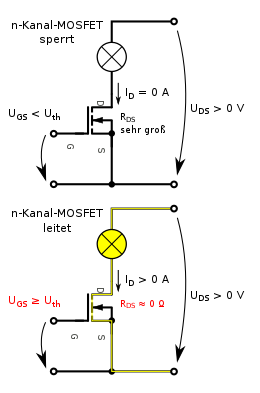

Wie andere Feldeffekttransistoren wirkt der MOSFET wie ein spannungsgesteuerter Widerstand, das heißt, über die Gate-Source-Spannung UGS kann der Widerstand zwischen Drain und Source RDS und somit der Strom IDS (vereinfacht ID) durch RDS um mehrere Größenordnungen geändert werden. Der Schlüssel zum Verständnis dieser Widerstandsänderung in einer MOS-Struktur liegt in der Entstehung (Anreicherungstypen) bzw. Abschnürung (Verarmungstypen) eines leitenden Kanals unter dem Gate (Details siehe unten).

Grundtypen

[Bearbeiten | Quelltext bearbeiten]Ähnlich wie der Bipolartransistor kann auch der MOSFET in die zwei grundlegenden Varianten p-Typ (auch p-leitend, p-Kanal oder PMOS) und n-Typ (auch n-leitend, n-Kanal oder NMOS) eingeteilt werden. Werden, beispielsweise in integrierten Digitalschaltungen, beide Typen gemeinsam verwendet, spricht man von CMOS (engl.: complementary MOS). Zusätzlich gibt es von beiden Varianten jeweils zwei Formen, die sich im inneren Aufbau und in den elektrischen Eigenschaften unterscheiden:

- Verarmungstyp (engl.: depletion) – auch selbstleitend, normal-an, normal leitend

- Anreicherungstyp (engl.: enhancement) – auch selbstsperrend, normal-aus, normal sperrend

In der Praxis werden mit großer Mehrheit Anreicherungstypen (=normal sperrend) eingesetzt.

Grundsätzlicher Aufbau und physikalische Funktion

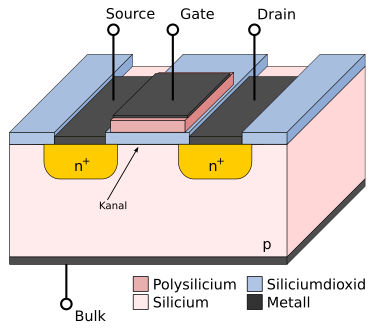

[Bearbeiten | Quelltext bearbeiten]Als Beispiel sei der selbstsperrende n-Kanal-MOSFET (Anreicherungstyp) gegeben.

Als Grundmaterial dient ein schwach p-dotierter Siliziumeinkristall (Substrat). In dieses Substrat sind zwei stark n-dotierte Gebiete eingelassen, die den Source- bzw. Drain-Anschluss erzeugen. Zwischen den beiden Gebieten befindet sich weiterhin das Substrat, wodurch eine npn-Struktur entsteht, die vorerst keinen Stromfluss zulässt (vgl. npn-Transistor: Ohne Basisstrom ist der Transistor gesperrt). Genau über diesem verbleibenden Zwischenraum wird nun eine sehr dünne, widerstandsfähige Isolierschicht (Dielektrikum, meist Siliziumdioxid) aufgebracht. Das Dielektrikum trennt die darüberliegende Gate-Elektrode vom Silizium (genauer vom Kanalgebiet). Als Gate-Material wurde bis Mitte der 1980er Aluminium verwendet, das von n+- bzw. p+-dotiertem (entartetem) Polysilizium (Abkürzung für polykristallines Silizium) abgelöst wurde.

Durch diesen Aufbau bilden Gate-Anschluss, Dielektrikum und Bulk-Anschluss einen Kondensator, der beim Anlegen einer positiven Spannung zwischen Gate und Bulk aufgeladen wird. Durch das elektrische Feld wandern im Substrat Minoritätsträger (bei p-Silizium Elektronen) an die Grenzschicht und rekombinieren mit den Majoritätsträgern (bei p-Silizium Defektelektronen). Das wirkt sich wie eine Verdrängung der Majoritätsträger aus und wird „Verarmung“ genannt. Es entsteht eine Raumladungszone an der Grenzschicht zum Oxid mit negativer Raumladung. Ab einer bestimmten Spannung Uth (engl. threshold voltage, Schwellspannung) ist die Verdrängung der Majoritätsladungsträger so groß, dass sie nicht mehr für die Rekombination zur Verfügung stehen. Es kommt zu einer Ansammlung von Minoritätsträgern, wodurch das eigentlich p-dotierte Substrat nahe an der Isolierschicht n-leitend wird. Dieser Zustand wird starke „Inversion“ genannt. Im Bändermodell erklärt, führt die erhöhte Gate-Spannung zu einer Bandbiegung von Leitungs- und Valenzband an der Grenzschicht. Das Ferminiveau liegt ab der kritischen Spannung näher am Leitungsband als am Valenzband. Das Halbleitermaterial ist somit invertiert. Der entstandene dünne n-leitende Kanal verbindet nun die beiden n-Gebiete Source und Drain, wodurch Ladungsträger (beinahe) ungehindert von Source nach Drain fließen können.

Prinzipiell sind Source- und Drain-Anschluss zunächst gleichwertig. Meist ist der Aufbau aber nicht symmetrisch, um ein besseres Verhalten zu erzielen. Außerdem wird bei den meisten Bauformen Bulk intern elektrisch mit Source verbunden, da ein Potentialunterschied zwischen Source und Bulk die Eigenschaften des Transistors (vor allem die Schwellenspannung) negativ beeinflusst (body effect). Auf die grundlegende Funktion hat diese Verbindung keinen Einfluss. Allerdings entsteht zusätzlich eine Diode zwischen Bulk- und Drain-Anschluss, die parallel zum eigentlichen Transistor liegt. Bulk mit dem p-dotierten Substrat und Drain mit dem n-Gebiet bilden den p-n-Übergang. Diese Inversdiode ist als Pfeil im Schaltsymbol des MOSFETs dargestellt. Er zeigt beim n-Kanal-MOSFET vom Bulk-Anschluss zum Kanal.

Zuordnung der Source- und Drain-Gebiete bei PMOS und NMOS

[Bearbeiten | Quelltext bearbeiten]

Source bezeichnet den Anschluss, von dem die für den Ladungstransport verantwortlichen Ladungsträger (Majoritätsladungsträger) im leitenden Fall in Richtung des Drain-Anschlusses driften.

Beim p-Kanal-MOSFET (PMOS, PMOSFET) bilden Defektelektronen (Löcher) die Majoritätsladungsträger, sie fließen in Richtung der technischen Stromrichtung.[5] Bei der Beschaltung von p-Kanal-MOSFET ist das Source-Potential (+, näher an gelegen) größer als das Drain-Potential (−; näher an gelegen).

Beim n-Kanal-MOSFET (NMOS, NMOSFET) bilden hingegen Elektronen die Majoritätsladungsträger.[5] Sie fließen entgegen der technischen Stromrichtung. Bezüglich des elektrischen Potentials ist daher die Lage von Source und Drain entgegengesetzt zum p-Kanal-MOSFET. Das heißt, das Source-Potential (−; näher an gelegen) ist geringer als das Drain-Potential (+; näher an gelegen).

Varianten

[Bearbeiten | Quelltext bearbeiten]Mit den steigenden Anforderungen an die elektrischen Eigenschaften von MOSFETs und der Notwendigkeit, mit den Effekten der Miniaturisierung bei den Transistoren (z. B. Kurzkanaleffekte) umzugehen, wurden in den vergangenen Jahrzehnten Varianten des planaren MOSFET entwickelt. Sie unterscheiden sich häufig in der Gestaltung des Dotierungsprofils oder der Materialwahl. Beispiele sind LDD-MOSFETs (von engl. lightly doped drain), Transistoren mit Halo-Implantaten oder gestrecktem Silizium sowie HKMG-Transistoren. Da in der Regel verschiedene Verbesserungen gleichzeitig genutzt werden, lässt sich hier jedoch keine Klassifikation anwenden.

Darüber hinaus ist zwischen lateralen (also parallel zu der Oberfläche ausgerichteten) und vertikalen Bauformen zu unterscheiden. Während laterale Transistoren vorwiegend in der Nachrichtentechnik zum Einsatz kommen (lateral double-diffused MOSFET, LDMOS[6]), findet sich die vertikale Bauform überwiegend in der Leistungselektronik wieder. Der Vorteil der vertikalen Struktur liegt in der höheren möglichen Sperrspannung der Bauelemente.

Schaltzeichen

[Bearbeiten | Quelltext bearbeiten]Als Schaltzeichen werden im deutschsprachigen Raum meist Darstellungen mit den vier Anschlüssen für Gate, Source, Drain und Body/Bulk (mittiger Anschluss mit Pfeil) genutzt. Dabei kennzeichnet die Richtung des Pfeils am Body/Bulk-Anschluss die Kanal-Art, das heißt die Majoritätsladungsträgerart. Hierbei kennzeichnet ein Pfeil zum Kanal einen n-Kanal- und ein Pfeil weg vom Kanal einen p-Kanal-Transistor. Ob der Transistor selbstsperrend oder selbstleitend ist, wird wiederum über eine gestrichelte („Kanal muss erst invertiert werden“ → Anreicherungstyp, selbstsperrend) bzw. eine durchgängige („Strom kann fließen“ → Verarmungstyp, selbstleitend) Kanallinie dargestellt. Darüber hinaus sind vor allem im internationalen Umfeld weitere Zeichen üblich, bei denen der üblicherweise mit Source verbundene Body/Bulk-Anschluss nicht dargestellt wird.[7] Die Kennzeichnung des Transistortyps erfolgt dann wiederum über Pfeile und unterschiedliche symbolische Darstellungen des Kanals sowie über einen Kreis am Gate, vgl. Tabelle. Zur Kennzeichnung der Source-Elektrode wird in manchen Symbolen der Kontakt zum Gate nicht mittig über dem Kanal, sondern direkt gegenüber dem Source-Anschluss dargestellt.

Schaltzeichen diskreter MOSFETs (Auswahl verschiedener Darstellungsvarianten) Leitungs- /

KanaltypAnreicherungstyp

(selbstsperrend)Verarmungstyp

(selbstleitend)p-Kanal

n-Kanal

Kennlinienfeld

[Bearbeiten | Quelltext bearbeiten]| Symbol | Berechnung | Beschreibung |

|---|---|---|

| Ausgangsspannung zwischen Drain und Source | ||

| Eingangsspannung zwischen Gate und Source | ||

| Spannung zwischen Source und Back-Gate, auch Bulk-Anschluss genannt | ||

| positive Versorgungsspannung aus NMOS, wird auch in CMOS-Technik verwendet | ||

| negative Versorgungsspannung aus NMOS, wird auch in CMOS-Technik verwendet |

Schwellenspannung

[Bearbeiten | Quelltext bearbeiten]Die Schwellenspannung (engl.: threshold voltage) stellt ein zentrales Element bei der Modellbetrachtung von MOSFETs dar und hängt stark von der Prozesstechnik ab. Dabei entscheiden die Dotierungen von Source, Drain und des Kanalgebietes über die Größe der Schwellenspannung.

- für NMOS-Verarmungstyp und PMOS-Anreicherungstyp

- für NMOS-Anreicherungstyp und PMOS-Verarmungstyp, typ. zwischen 1 V und 3 V.

Zudem ist die Schwellenspannung abhängig von der Temperatur. Für die Beschreibung reicht die Abhängigkeit 1. Ordnung (lineare Abhängigkeit):

wobei der Temperaturkoeffizient, die Temperatur und die Stütztemperatur (beispielsweise die typische Betriebstemperatur) ist.

Ausgangskennlinienfeld

[Bearbeiten | Quelltext bearbeiten]

Die Darstellung der Zusammenhänge zwischen dem Drain-Strom (auch , Drain-Source-Strom) und der Drain-Source-Spannung in Abhängigkeit von der Gate-Source-Spannung wird als Ausgangskennlinienfeld eines MOSFETs bezeichnet. Es ist für alle MOSFETs (NMOS-Anreicherungstyp, NMOS-Verarmungstyp, PMOS-Anreicherungstyp und PMOS-Verarmungstyp) prinzipiell gleich. Unterschiede ergeben sich nur in den Potentialbezugspunkten von Drain und Source sowie im Vorzeichen des Verstärkungsfaktors. Die Kennlinien werden durch weitere Effekte (Temperatur, Substratvorspannung, Kurzkanaleffekte etc.) beeinflusst.

Die einzelne ID-UDS-Kennlinie eines MOSFETs unterteilt sich in drei Bereiche: den Sperrbereich, den aktiven Bereich und den Sättigungsbereich.

Sperrbereich

[Bearbeiten | Quelltext bearbeiten]Im Sperrbereich (engl. cutoff region), auch Abschaltbereich oder Unterschwellenbereich (engl. subthreshold region) genannt, liegt die Gate-Source-Spannung unterhalb der Schwellenspannung .

Für gilt:

mit

- dem Schwellenspannungsstrom (engl.: threshold current)

- dem subthreshold swing (Kehrwert von subthreshold slope, Unterschwellensteilheit)

- der Temperaturspannung ,

- der Boltzmannkonstante ,

- die Ladung der beteiligten Ladungsträger (≙ Elementarladung),

- dem Emissionsfaktor im Unterschwellenbereich[8] (engl. sub-threshold slope factor) und

- der Verarmungskapazität (engl.: depletion capacitance), diese setzt sich aus den Überlappkapazitäten an Drain und Source zusammen

Der Leckstrom (engl.: leakage current) eines Anreicherungs-MOSFET berechnet sich aus der Gleichung für den Sperrbereich:

- (nur für NMOS-Anreicherungs- und PMOS-Anreicherungs-Typ).

Triodenbereich

[Bearbeiten | Quelltext bearbeiten]Im Triodenbereich (auch aktiver Bereich genannt, engl.: triode region) liegt die Gate-Source-Spannung über der Schwellenspannung (Im Fall des Anreicherungs-MOSFET), sodass ein durchgehender Kanal zwischen Drain und Source entsteht. Der erste Abschnitt des Triodenbereiches, in dem das Verhältnis von Drain-Strom IDS zu Drain-Source-Spannung UDS noch linear angenähert werden kann, wird auch als linearer Bereich bezeichnet (auch ohmscher Bereich, engl.:linear region or ohmic region). Der Bereich wird durch die Kennlinie der Grenzspannung begrenzt.

Die Bezeichnung stammt von dem Umstand, dass die Kennlinien bei nahezu linear durch den Ursprung verlaufen, was dem Verhalten eines ohmschen Widerstands entspricht.

Für und gilt:

mit

- dem NMOS-Verstärkungsfaktor (n-dotiert) ,

- dem PMOS-Verstärkungsfaktor (p-dotiert) ,

- der Ladungsträgerbeweglichkeit der Elektronen in n- bzw. p-dotiertem Substrat bzw.

- der flächenspezifische Kapazität des Gate-Kondensators

- der Weite und der Länge des Gates,

- der Dicke des Gate-Dielektrikums,

- der Permittivität des jeweiligen Materials, z. B. Silizium als Substrat und Siliziumdioxid als Dielektrikum

Sättigungsbereich

[Bearbeiten | Quelltext bearbeiten]Im Sättigungsbereich (engl. saturation region, active mode, Abschnürbereich genannt) verläuft die IDS-UDS-Kennlinie näherungsweise parallel zur -Achse. Das heißt, wird die Spannung zwischen Drain und Source erhöht, hat dies kaum einen steigernden Effekt auf den Strom, der zwischen diesen Kontakten fließt. Die Grenze, ab der sich dieses Verhalten zeigt, wird als definiert. Wie im Ausgangskennlinienfeld zu sehen, kann allerdings die Eingangsspannung genutzt werden, um den Strom direkt zu beeinflussen. In diesem Fall verhält sich der Transistor wie eine durch die Eingangsspannung gesteuerte Stromquelle.[9] Weitere Effekte entstehen durch die Kanallängenmodulation.

Falls die Eingangsspannung am Transistor oberhalb der Threshold-Spannung liegt:

- ,

und die Ausgangsspannung oberhalb der Sättigungsspannung (bzw. Abschnürspannung) liegt:

dann gilt für den Strom im Ausgangskreis:

Beim Vergleich mit einem Bipolartransistor muss bei der Verwendung des Begriffs Sättigungsbereich darauf geachtet werden, dass der Begriff Sättigung beim Bipolartransistor eine andere Bedeutung hat.

Kennlinieneffekte

[Bearbeiten | Quelltext bearbeiten]Substratvorspannung, Back-Gate-Steuerung, Body-Effekt

[Bearbeiten | Quelltext bearbeiten]Wenn eine Substratvorspannung (auch Back-Gate-Spannung) an den Transistor angelegt wird, so hängt die Schwellenspannung von der Source-Bulk-Spannung ab. Je größer die Spannung wird, desto größer wird die Schwellenspannung.

mit

- dem Substrateffekt-Parameter ,

- dem Oberflächenpotential bei starker Inversion: ,

- der Dotierungskonzentration des Substrats bzw. der n- oder p-Wanne (typische Werte bewegen sich im Bereich 1013 bis 1017 cm−3) und

- der Eigenleitkonzentration des undotierten (intrinsischen) Substratmaterials (z. B. 1010 cm−3 Silizium bei Raumtemperatur).

Kanallängenmodulation

[Bearbeiten | Quelltext bearbeiten]Unter dem Begriff Kanallängenmodulation wird ein Effekt verstanden, der in seinen Auswirkungen dem Early-Effekt der Bipolartransistoren gleicht. Die Kanallängenmodulation tritt im Sättigungsbereich () auf und modelliert die Einschnürung des Kanals (der Kanal erreicht das Drain nicht mehr, die Region ohne Kanal wird auch Pinch-Off-Region genannt). In der Ausgangskennlinie ist die Kanallängenmodulation durch den Anstieg des Drainstromes im Sättigungsbereich bei zunehmender Drain-Source-Spannung zu erkennen (DIBL-Effekt). Spürbare Auswirkungen zeigt die Kanallängenmodulation bei Strukturgrößen von L < 1 µm. In Näherung lässt sich diesem Effekt durch folgende Näherungsgleichung Rechnung tragen, wobei der Kanallängenmodulationsparameter das Ausmaß charakterisiert:[10]

wobei der Transistorstrom ohne Berücksichtigung ist. Es gilt:

- .

„Threshold-Voltage-roll-off“-Effekt

[Bearbeiten | Quelltext bearbeiten]

Bei kurzen Kanälen beeinflusst ein Effekt höherer Ordnung die Schwellenspannung, dieser wird „Threshold-Voltage-roll-off“-Effekt genannt. Dabei beeinflusst die Kanallänge die Schwellenspannung:

- mit

Breite der Raumladungszone am Drain:

Schaltbetrieb

[Bearbeiten | Quelltext bearbeiten]

Beim Schalten eines MOSFETs wirken sich primär die Streukapazitäten innerhalb des Bauteils auf das zeitliche Verhalten aus. Wesentlichen Einfluss auf die Schaltzeiten besitzt die sogenannte Miller-Kapazität, eine parasitäre Kapazität zwischen der Gate-Elektrode zur Drain-Elektrode. Für die Modellbetrachtung des Schaltverhaltens dienen die Parameter CGS, CDS und CDG (siehe Bild), wohingegen in Datenblättern Ciss, Coss und Crss angegeben sind. Das liegt daran, dass letztere einfach messbare Größen darstellen. Nachfolgende Formeln ermöglichen die Umrechnung zwischen beiden Systemen:

Der Einschaltvorgang teilt sich in drei Abschnitte auf (siehe auch Bild unten):

- : Gate-Source-Kapazität aufladen (Totzeit)

- : Miller-Kapazität entladen

- : Gate-Source-Kapazität aufladen und voll durchschalten

Während der ersten Phase steuert der MOSFET noch nicht durch, denn zunächst muss die Gate-Source-Kapazität bis zum Erreichen der Schwellspannung aufgeladen werden. Ab dem Punkt t2 beginnt die Drain-Source-Strecke durchzusteuern. Dabei muss der Treiber auch den Entladestrom für die Drain-Gate-Kapazität abführen. Dabei stellt sich ein Gleichgewicht ein, denn je höher UGS steigt, desto schneller fällt UDS und damit UDG, wodurch ein höherer Entladestrom fließt. Die Gate-Source-Spannung bildet zeitlich ein Plateau (Miller-Plateau), weil die Drain-Gate-Spannung einem weiteren Anstieg entgegenarbeitet. Die Stärke dieses Effektes hängt folglich direkt mit der Höhe der Versorgungsspannung (USupply) zusammen.

- für

Die letzte Phase sorgt für das vollständige Durchschalten des Transistors, damit ein minimaler Drain-Source-Widerstand (RDSon) erreicht wird. Dadurch verringern sich die ohmschen Verluste, und ein hohes On/Off-Verhältnis, sprich ein hoher Wirkungsgrad, wird erzielt.

Der Ausschaltvorgang verläuft umgekehrt, jedoch sind die Zeiten nicht identisch. Die Ausschaltzeit ist dabei immer etwas länger als die Einschaltzeit, was häufig in Leistungs-Gegentakt-Endstufen durch entsprechende Totzeiten in der Ansteuerung berücksichtigt werden muss.

Das gezeigte Modell stellt eine starke Vereinfachung dar und dient dem grundlegenden Verständnis für das Schaltverhalten eines MOSFETs, was für viele Anwendungen auch hinreichend ist. Für detaillierte Betrachtungen muss die Spannungsabhängigkeit der Kapazitäten herangezogen werden[12] sowie die Auswirkung weiterer parasitärer „Bauelemente“. Statt der Gate-Source-Kapazität wird die Gate-Ladung QG betrachtet.

Inversdiode

[Bearbeiten | Quelltext bearbeiten]Eine Spannung zwischen Source und dem Substrat bewirkt eine Verschiebung der Schwellenspannung. Je höher diese Spannung ist, desto höher wird die Spannung, die zwischen Gate und Source erforderlich ist, damit der Kanal leitend wird. Dieser als Body-Effekt bekannte Einfluss ist in den meisten Anwendungen unerwünscht. Daher ist üblicherweise das Substrat direkt im Transistor elektrisch mit Source verbunden. Auf diese Weise liegen Substrat und Source zwangsweise auf dem gleichen elektrischen Potential. Als Nebenwirkung dieser Verbindung liegt ein p-n-Übergang zwischen Source und Drain, das notwendigerweise gegensätzlich zum Substrat dotiert ist. Dieser Übergang wird leitend, wenn Drain und Source hinsichtlich ihres Potentials die Rollen tauschen. Das ist bei n-Kanal-MOSFETs der Fall, wenn von außen an Source eine höhere Spannung angelegt wird als an Drain. Da dies die umgekehrte Richtung wie im normalen Betrieb ist, wird der p-n-Übergang auch Inversdiode genannt. Eine andere Bezeichnung für den Übergang ist Body-Diode.

Ein MOSFET kann nur in Sperrrichtung der Inversdiode als regelbarer Widerstand eingesetzt werden. Als Schaltelement kann ein MOSFET ebenfalls nur in einer Richtung einen Stromfluss unterbinden. Viele Schaltungen sind daher so ausgelegt, dass die Inversdiode nie in Durchlassrichtung betrieben wird. Beispiele dafür sind die Endstufen von Audioverstärkern, oder die Transistoren, die in Computern digitale Signale schalten.

Bei manchen Schaltanwendungen ist eine Leitung von Strom entgegen der „normalen“ Richtung sogar erwünscht. So sind Brückenschaltungen so konzipiert, dass die Inversdiode leitend wird. Bei Anwendungen mit hoher Schaltfrequenz ist allerdings die vergleichsweise lange Sperr-Erholzeit der Inversdiode eine Begrenzung. Außerdem führt ihre recht hohe Flussspannung zu erhöhter Verlustleistung. In diesen Fällen wird extern eine schnelle Schottkydiode mit niedrigerer Flussspannung parallel zur Inversdiode an Source und Drain hinzugefügt.

Bei FREDFETs zeigt die Inversdiode ein besseres Schaltverhalten und ermöglicht somit einen kompakteren Aufbau.

Leckströme

[Bearbeiten | Quelltext bearbeiten]Bei den Leckströmen handelt es sich um unerwünschte Stromflüsse innerhalb der Transistoren. Diese treten sowohl im gesperrten als auch im leitenden Zustand des Transistors auf. Momentan (Stand 2008) sind hier vor allem der subthreshold leakage (frei übersetzt: Unterschwellspannungsleckstrom), junction leakage als auch der Gate-Oxid-Leckstrom dominierend.

In konventionellen CMOS-Techniken mit Siliziumdioxid als Dielektrikum stellen die Leckströme eines der Hauptprobleme beim Chipentwurf dar, wenn Transistoren mit Gatelängen von weniger als 100 nm verwendet werden (praktisch alle 2010 aktuellen Prozessoren).[13] So verursachten die Leckströme Mitte der 2000er-Jahre bei Prozessoren im High-End-Bereich bis zur Hälfte des Gesamtenergieverbrauchs.[14][15] Eine Variante zur Reduzierung der Leckströme ist die sogenannte High-k+Metal-Gate-Technik, bei der dielektrische Materialien mit hoher Permittivität (High-k-Dielektrikum) statt Siliziumdioxid genutzt werden, beispielsweise dotiertes Hafniumoxid.

Verwandte Transistorvarianten

[Bearbeiten | Quelltext bearbeiten]

Neben den konventionellen MOSFET-Varianten in Planartechnik, die weiterhin für typische CMOS-Schaltkreise genutzt werden, existieren noch diverse Spezialvarianten mit verändertem Aufbau. Sie werden für andere Anwendungen als digitale Logik (z. B. höhere Ausgangsspannungen für Treiberschaltungen oder hohe Leistungen) oder zur Verbesserung des Schaltverhaltens bei kleineren Strukturgrößen eingesetzt, was jedoch mit zum Teil deutlich erhöhtem Herstellungsaufwand verbunden ist. Beispiele sind Hochspannungstransistoren, lateraler DMOS-FET (LDMOSFET) und Drain-erweiterter MOSFET (DEMOSFET), Leistungs-MOSFET (z. B. in der Bauform VMOS-, UMOS-, TrenchMOS-FET) sowie Multigate-Feldeffekttransistoren (MuFET), wie der FinFET.

Drain-erweiterter MOSFET

[Bearbeiten | Quelltext bearbeiten]Der Drain-erweiterte MOSFET (DE-MOSFET, von engl. drain-extended MOSFET) ist kompatibel mit der CMOS-Planartechnik und kann daher im selben monolithischen integrierten Schaltkreis eingesetzt werden. Kernelement des DEMOSFET ist ein niedriger dotierte Driftzone zwischen dem eigentlichen Drainanschluss und dem entgegengesetz dotiertem Gebiet unter der Gate-Elektrode. Die mit diesem Transistor zu schaltende Source-Drain-Spannung fällt zu großteilen über diese Driftzone hinweg ab, so dass unter der Gate-Elektrode nur noch verhältnismäßig kleine Spannungen auftreten, die unproblematisch für einen Gate-Drain-Durchbruch des Dielektrikums sind. Um das zu erreichen wird das üblicherweise zur Kontraktierung und Potentialverteilung genutzte Silizid über dem Driftbereich bewusst herausgehalten.

DEMOSFET können sowohl als p-Kanal- (DEPMOS-FET) sowie als n-Kanal-DEMOSFETs (DENMOS-FET) gefertigt werden. Zudem gibt es diverse Abwandlungen um höhere Source-Drain-Spannungen zu erlauben, z. B. mit STI oder LOCOS zwischen Gate und Drain oder symmetrische DEMOS mit Driftzonen im Drain- und Source-Bereich. Drain-erweiterte Transistoren werden unter anderem in Analog- und Power-Management-Designs verwendet. Die genutzten Spannungen hängen von den genutzten Gateoxid-Dicken ab und liegen für typische 130-nm- und 180-nm-Prozessen im Bereich von 20 bis 40 V (ggf. auch höher). Bei kleineren Technologieknoten sinkt dieser Wert deutlich.[16]

Lateraler DMOS-FET

[Bearbeiten | Quelltext bearbeiten]Der laterale doppelt-diffundierte MOSFET (LDMOS-FET, von engl. lateral double-diffused MOSFET) ist eine MOSFET-Variante zum Schalten höherer Spannungen. Kernelement des LDMOSFET ist ein selbstjustierender p-leitender Kanal in einer n-dotierten Wanne eines p-dotierten Silizium-Substrats. Der Kanal entsteht durch die Kombination von Bor- und Arsen-Implantation, die aufgrund unterschiedlicher Diffusionskoeffizienten bei den nachfolgenden Temperaturschritten (z. B. Aktivierung und Ausheilen der Kristallschäden) unterschiedlich weit diffundieren (sozusagen doppelt diffundiert). So bildet sich in der n-Wanne eine p-dotierte Wanne (back gate oder body genannt) die das n-dotierte (Arsen) Source-Gebiet umschließt. Oberhalb des p-dotierten Kanals wird der für MOSFETs typische Schichtstapel aus einer dünnen Nichtleiterschicht (z. B. Gate-Oxid) und der Gate-Elektrode (z. B. Polysilizium) abgeschieden, der deutlich größer als die physikalische Kanallänge ist und das Schaltverhalten kontrolliert. Das Drain-Gebiet auf der anderen Seite des Gates ist abermals ein hochdotierter n-Bereich.

Die elektrischen Eigenschaften dieser Struktur können durch diverse Maßnahmen verändert werden. Dazu zählt beispielsweise:

- die elektrische Verbindung des Bor-dotierten Back-Gates bzw. Body mit dem Source-Anschluss, um die Flächeneffizienz und den Körperwiderstand zu reduzieren.

- das Hinzufügen einer „vergrabenen“ n+-dotierten Schicht um die Struktur zu isolieren und Einflüsse parasitärer Halbleiterstrukturen zu minimieren.

- das Hinzufügen tiefer n-dotierter Drain-Gebiete um die Effizienz durch einen geringeren Widerstand zu verringern.

- das Hinzufügen von dickeren Nichtleiter-Schichten unter dem Gate auf der Drain-Seite oder einer Feldplatte, um durch eine höhere Durchbruchsspannung die Nutzung von höheren Ausgangsspannungen zu ermöglichen.

- die Erhöhung der elektrischen Leitfähigkeit im n-dotierten Drift-Bereich auf der Drain-Seite, um den Einschaltwiderstand (RON) zu reduzieren.

- die Variante kann kompatibel mit der CMOS-Planartechnik gefertigt werden und daher im selben monolithischen integrierten Schaltkreis eingesetzt werden.

LDMOS-Transistoren gibt es in vertikaler und lateraler Bauform. Eingesetzt werden LDMOS-Komponenten in der Regel in integrierten Leistungs-Verstärkern (MMIC) von 100 MHz bis 3 GHz, wie z. B. Mobilfunkstationen. Laterarale LDMOS werden oft im Rahmen von Mix-Signal-Schaltkreise für High-Side- als auch für Low-Side-Treiber und Brückenschaltungen mit höheren Spannungen (20–100 V sind typisch) eingesetzt. Ein Vorteil gegenüber lateralen DEMOS-Transistoren ist die Schaltung höherer Ströme.[17]

FinFET

[Bearbeiten | Quelltext bearbeiten]FinFETs sind eine Gruppe von nicht-planaren MOSFETs, bei denen sich der leitfähige Kanal an einem dünnen Grat (englisch fin) aus Silicium befindet. Die Bezeichnung wurde erstmals 1999 in einer Veröffentlichung von Forschern der University of California, Berkeley verwendet und basiert auf dem Einzelgatetransistordesign DELTA.[18] Da sich der Kanal prinzipiell an allen Seiten des Grats befinden kann, werden oft auch Multigate-Feldeffekttransistoren wie der Dual- (Tetrode) oder Tri-Gate-MOSFET als FinFET bezeichnet.[19][20]

FinFETs bieten die Vorteile eines vergrößerten Kanalbereichs und besserer elektrischer Eigenschaften (z. B. kurze Schaltzeiten oder kleinere Leckströme). Zudem benötigen sie bei gleicher Leistungsfähigkeit weniger Platz, was eine höhere Integrationsdichte erlaubt. Eingesetzt werden sie zum Beispiel in HF-Schaltungen (HF-Verstärker, multiplikativer Mischer). Aber auch für Standardlogikschaltungen, wie Hauptprozessoren oder Mikrocontroller, werden diese alternativen Transistorvarianten zunehmend interessant. Intel setzt seit 2012 mit der 22-nm-Technologie Ivy Bridge erstmals FinFETs in der Massenproduktion für Prozessoren ein. Seit 2014 bietet auch TSMC einen 16-nm-FinFET-Prozess für die Halbleiterindustrie an;[21] ab 2022 plant das Unternehmen die 3-nm-Volumenfertigung.[22]

-

Prinzipieller Aufbau eines n-Kanal-MOSFETs im Querschnitt (Planartechnik)

-

Schema eines FinFET („Dual-Gate“)

-

Darstellung eines Dual-Gate-MOSFET BF981 (oder ähnlicher Typ). Im Schaltsymbol wurden die Schutzdioden an den Gates weggelassen.

Vor- und Nachteile

[Bearbeiten | Quelltext bearbeiten]Ein prinzipieller Nachteil der MOSFET-Technik ist die geringe Oberflächenbeweglichkeit der Ladungsträger im Kanal. Elektronen besitzen dabei eine höhere Beweglichkeit als Defektelektronen, daher haben n-Kanal-MOSFET bessere Eigenschaften als p-Kanal-Typen. Durch die Verkleinerung der Bauelementstrukturen lässt sich dieser Nachteil jedoch ausgleichen und die Schaltgeschwindigkeit erhöht sich. Dadurch gelingt es einerseits, schnellere Einzeltransistoren herzustellen, andererseits lassen sich durch feine Wabenstrukturen auch schnelle MOSFET für große Ströme herstellen. Durch Skalierung in den Submikrometerbereich wird der MOSFET für integrierte digitale Anwendungen mit Taktfrequenzen oberhalb von 1 GHz verwendbar. MOSFETs sind wegen ihres einfachen Herstellungsprozesses (CMOS-Prozess) und der lateralen Struktur besonders für integrierte Schaltungen geeignet.

Da bei IGFETs im Gegensatz zu Bipolartransistoren die Steuerung nicht über einen Stromfluss (Basisstrom), sondern über eine Steuerspannung erfolgt, werden sie irreführenderweise als „stromlos“ bezeichnet. Im statischen Betrieb, d. h., bei konstanter Gate-Spannung, fließt über das Gate so gut wie kein Strom. Allerdings ist zur Umladung der Gate-Kapazität ein teilweise erheblicher Lade- und Entladestrom notwendig. Diese Ströme verursachen zusammen mit den Gate-Leckströmen, die bei heutigen Mikroprozessoren nicht mehr vernachlässigbar sind, die hohe Leistungsaufnahme moderner integrierter Schaltkreise.

In Leistungsanwendungen ist der Leistungs-MOSFET hinsichtlich kurzer Schaltzeiten und geringer Schaltverluste den Bipolartransistoren und IGBTs überlegen. Er erreicht jedoch nicht deren hohe Sperrspannungen. Gegenüber bipolarer Technik besitzt die Drain-Source-Strecke des MOSFET eine reine Widerstandscharakteristik, die den statischen Spannungsabfall und die statische Verlustleistung im Betrieb bestimmt. Erst dadurch werden die hohen Wirkungsgrade von leistungselektronischen Schaltungen besonders bei niedrigen Spannungen und Batteriebetrieb möglich (vgl. Synchrongleichrichter).

Im Gegensatz zu bipolaren Transistoren besitzt der Kanalwiderstand der Drain-Source-Strecke des MOSFET einen positiven Temperaturkoeffizienten. Das bedeutet, dass bei steigender Temperatur auch der Widerstand steigt. Dadurch kann man mehrere MOSFETs bei reinen Schaltanwendungen oft ohne zusätzliche symmetrierende Maßnahmen parallelschalten, um die Stromtragfähigkeit zu erhöhen und den Spannungsfall zu verringern. Sobald einer der MOSFETs durch zu viel Strom zu heiß wird, steigt sein Widerstand. Dadurch reduzieren sich bei MOSFETs Unterschiede der Stromverteilung statt wie bei polaren Transistoren sich zu vergrößern.

Leistungs-MOSFETs auf Siliziumbasis werden vorteilhaft beim Schalten von Spannungen bis 800 V und Strömen von bis zu mehreren hundert Ampere eingesetzt. Einsatzgebiete sind u. a. Schaltnetzteile, Synchrongleichrichter, getaktete Strom- und Spannungsregler und auch starke Hochfrequenzsender bis in den UKW-Bereich. In Sonderanwendungen werden Schaltzeiten von nur einigen Nanosekunden bei Spannungen von mehreren Kilovolt durch Reihenschaltung realisiert.

Handhabung

[Bearbeiten | Quelltext bearbeiten]MOSFETs weisen durch die sehr hochohmige Isolierung des Gates gegenüber dem Source-Drain-Kanal eine große Empfindlichkeit gegenüber elektrostatischen Entladungen (engl. electro-static discharge, ESD) auf. Das führt bei unsachgemäßer Handhabung von elektronischen Bauteilen, die aus Feldeffekttransistoren bestehen, zu einem Durchbruch der Gate-Isolierschicht und damit zur Zerstörung der Feldeffekttransistoren. Die daraus resultierenden Schwierigkeiten bei der Handhabung waren einer der Gründe, warum Feldeffekttransistoren sich gegenüber Bipolartransistoren erst einige Jahrzehnte später am Markt durchsetzen konnten. Vielfach konnten schützende Drahtbrücken zwischen Gate und Source (Drain, Bulk) erst nach Einlötung des MOSFETs in der Anwendungsschaltung entfernt werden. Prinzipiell sind jedoch Leistungs-MOSFETs auf Grund ihrer meist im Nanofaradbereich liegenden Gatekapazität ausreichend gegen elektrostatische Aufladung natürlich geschützt, so dass besondere Schutzmaßnahmen – wie externe Drahtbrücken – hier meist nicht mehr benötigt werden. Heutige diskrete Kleinleistungs-Feldeffekttransistoren und integrierte Schaltungen haben außerdem meist integrierte Schutzdioden mit Widerständen oder entsprechende Halbleiterstrukturen an den Anschlussleitungen, welche die Auswirkungen von elektrostatischen Entladungen auf die empfindliche Gate-Isolierschicht minimieren. Trotzdem müssen bei der Handhabung von Feldeffekttransistoren immer noch besondere Vorsichtsmaßnahmen zur Vermeidung von elektrostatischen Aufladungen getroffen werden. So sind beispielsweise Arbeits- und Fertigungsbereiche, in denen mit Feldeffekttransistoren gearbeitet wird, durch ESD-Warnschilder gekennzeichnet. Zusätzlich sind immer die Herstellerangaben zu beachten.

Siehe auch

[Bearbeiten | Quelltext bearbeiten]Literatur

[Bearbeiten | Quelltext bearbeiten]- Hans-Joachim Fischer, Wolfgang E. Schlegel: Transistor- und Schaltkreistechnik. 4. Auflage. Militärverlag der DDR, Berlin 1988.

- Hans-Günther Wagemann, Tim Schönauer: Silizium-Planartechnologie. Grundprozesse, Physik und Bauelemente. Teubner, Stuttgart/Leipzig/Wiesbaden 2003, ISBN 3-519-00467-4.

Weblinks

[Bearbeiten | Quelltext bearbeiten]- Java-Applet zu NMOS

- Elektronik-Kompendium – MOS-Feldeffekttransistor (MOS-FET)

- Computer History Museum: [1]. Auf: computerhistory.org.

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Jared Walton: Nvidia Unveils Its Next-Generation 7nm Ampere A100 GPU for Data Centers, and It's Absolutely Massive In: Tom’s Hardware, 14. Mai 2020

- ↑ Patent US1745175: Method and Apparatus For Controlling Electric Currents. Erfinder: J. E. Lilienfeld (PDF).

- ↑ Martin (John) M. Atalla. National Inventors Hall of Fame, 2009, abgerufen am 21. Juni 2013.

- ↑ Sami Franssila: Introduction to Microfabrication. John Wiley and Sons, 2010, ISBN 978-0-470-74983-8, S. 229.

- ↑ a b Yaduvir Singh, Swarajya Agnihotri: Semiconductor Devices. I. K. International Pvt Ltd, 2009, ISBN 978-93-8002612-1, S. 128–130.

- ↑ Microwave Encyclopedia, Microwaves101.com: LDMOS ( des vom 14. Dezember 2008 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis., abgerufen am 29. Nov. 2008

- ↑ vgl. Michael Reisch: Halbleiter-Bauelemente. Springer, 2007, ISBN 978-3-540-73200-6, S. 219 (eingeschränkte Vorschau in der Google-Buchsuche).

- ↑ Ulrich Tietze, Ch. Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6, S. 204.

- ↑ Michael Reisch: Halbleiter-Bauelemente. Springer, 2007, ISBN 978-3-540-73199-3, S. 226.

- ↑ Kurt Hoffmann: Systemintegration : vom Transistor zur großintegrierten Schaltung. 2., korrigierte und erw. Auflage. Oldenbourg, München [u. a.] 2006, ISBN 3-486-57894-4, 4.5.2 Kanallängenmodulation, S. 188–190.

- ↑ Carl Walding: Nicht nur Verluste minimiert (Seite nicht mehr abrufbar, festgestellt im Mai 2019. Suche in Webarchiven) Info: Der Link wurde automatisch als defekt markiert. Bitte prüfe den Link gemäß Anleitung und entferne dann diesen Hinweis.. elektroniknet.de. Abgerufen am 20. September 2008.

- ↑ Martin Stiftinger: Simulation und Modellierung von Hochvolt-DMOS-Transistoren. Dissertation, TU Wien, 1994.

- ↑ Gordon Moore: No Exponential is Forever … but We Can Delay ’Forever’. International Solid State Circuits Conference (ISSCC), USA, 2003

- ↑ Y. S. Borkar: VLSI Design Challenges for Gigascale Integration. '18th Conference on VLSI Design, Kolkata, India, 2005

- ↑ ITRS – International technology roadmap for semiconductors 2006 Update.Technischer Report, 2006

- ↑ Badih El-Kareh, Lou N. Hutter: Silicon Analog Components : Device Design, Process Integration, Characterization, and Reliability. 2nd Auflage. Springer, Cham 2020, ISBN 978-3-03015085-3, S. 330 ff.

- ↑ Badih El-Kareh, Lou N. Hutter: Silicon Analog Components : Device Design, Process Integration, Characterization, and Reliability. 2nd 2020 Auflage. Springer, Cham 2020, ISBN 978-3-03015085-3, Chapter 7 High-Voltage and Power Transistors.

- ↑ Xuejue Huang u. a.: Sub 50-nm FinFET: PMOS. In: Electron Devices Meeting, 1999. IEDM Technical Digest. International. 1999, S. 67–70, doi:10.1109/IEDM.1999.823848.

- ↑ D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T. J. King, J. Bokor, C. Hu: FinFET-a self-aligned double-gate MOSFET scalable to 20 nm. In: Electron Devices, IEEE Transactions on. Band 47, Nr. 12, 2000, S. 2320–2325, doi:10.1109/16.887014 (PDF).

- ↑ E.J. Nowak, I. Aller, T. Ludwig, K. Kim, R.V. Joshi, Ching-Te Chuang, K. Bernstein, R. Puri: Turning silicon on its edge – double gate CMOS/FinFET technology. In: IEEE Circuits and Devices Magazine. Band 20, Nr. 1, 2004, S. 20–31, doi:10.1109/MCD.2004.1263404.

- ↑ FinFET-Monopol gebrochen – FinFETs für alle. Abgerufen am 4. Januar 2014.

- ↑ TSMC will mit 3 nm 2022 in die Volumenfertigung. In: PCGH Online (PC Games Hardware). Computec Media GmbH, 25. August 2020, abgerufen am 30. August 2020.