Und-Gatter

| Gatter-Typen | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

| AOI | OAI |

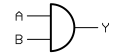

Ein Und-Gatter ist ein Gatter mit mehreren Eingängen und einem Ausgang, bei dem der Ausgang eine 1 liefert, wenn an allen Eingängen 1 anliegt. Es entspricht dem Logischen UND. In der Schaltalgebra wird die UND-Verknüpfung durch • (Mal), & oder ∧ dargestellt und wird auch als Konjunktion bezeichnet.

Übersicht

[Bearbeiten | Quelltext bearbeiten]| Funktion | Schaltsymbol | Wahrheitstabelle | Relais-Logik | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (vor 1976) | ||||||||||||||||||

|

|

|

| |||||||||||||||||

Und-Gatter mit größerer Anzahl von Eingängen

[Bearbeiten | Quelltext bearbeiten]Ein Und-Gatter hat standardmäßig zwei Eingänge (AND2), jedoch stehen auch Und-Gatter mit mehr als zwei Eingängen im Handel zur Verfügung. Die Schaltsymbole entsprechen dem eines AND2-Gatters mit zusätzlichen Eingängen.

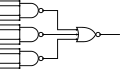

Die untenstehende Abbildung zeigt links ein Und-Gatter mit drei Eingängen (AND3) und in der Mitte einen möglichen Aufbau eines AND3-Gatters: Der Ausgang des ersten Und-Gatters wird an einen Eingang des zweiten angeschlossen.

In Logikfamilien wie CMOS können Und-Gatter effizienter durch Kaskadierung von NAND- und NOR-Gattern implementiert werden. Dies benötigt weniger Transistoren und ist deutlich schneller als eine entsprechende Kaskadierung von Und-Gattern.[1] Ein Beispiel ist in der rechten Abbildung dargestellt.

-

Schaltsymbol AND3

-

Möglicher Aufbau eines AND3-Gatters

-

UND-Gatter mit 12 Eingängen, realisiert mit NAND- und NOR-Gattern

Realisierung

[Bearbeiten | Quelltext bearbeiten]UND-Gatter werden als integrierte Schaltung (IC) von vielen Herstellern produziert. Standardbausteine dieser Art sind z. B. unter der Bezeichnung „7408“ in TTL-Technik und als „74HC08“ in CMOS-Technologie erhältlich und beinhalten vier UND-Gatter mit jeweils zwei Eingängen. Die genaue Bauteilbezeichnung ist herstellerabhängig. Logik-Gatter dieser Art sind für wenige Cent im Elektronik-Fachhandel erhältlich.

CMOS

[Bearbeiten | Quelltext bearbeiten]Das Bild rechts zeigt das Schaltbild eines Und-Gatters in CMOS-Technologie. Liegt an den Eingängen A und B High-Potential an, dann leiten T3 und T4, wobei T1 und T2 sperren. Dadurch liegt an T5 und T6 Low-Potential an und T5 leitet und T6 sperrt, weswegen am Ausgang Y High-Potential anliegt. Bei allen anderen Eingangszuständen liegt Low-Potential am Ausgang, weil T6 leitet.

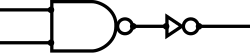

T1 bis T4 bilden hierbei ein NAND-Gatter und T5 und T6 einen Inverter. Dies ist unten links dargestellt. Durch die zusätzlich erforderlichen Transistoren und die dadurch verursache zusätzliche Laufzeit ist ein AND-Gatter in CMOS weniger effizient als ein NAND-Gatter.

-

UND-Gatter aus einem NAND-Gatter und einem Inverter

-

Schaltbild eines UND-Gatters in CMOS

Literatur

[Bearbeiten | Quelltext bearbeiten]- Ulrich Tietze, Christoph Schenk: Halbleiter-Schaltungstechnik. 12. Auflage. Springer, 2002, ISBN 3-540-42849-6.

Weblinks

[Bearbeiten | Quelltext bearbeiten]Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Norman Hendrich: AND gate (12 inputs). Universität Hamburg, abgerufen am 4. Februar 2024.