Serial Peripheral Interface

Das Serial Peripheral Interface (SPI) ist ein im Jahr 1987 von Susan C. Hill und anderen beim Halbleiterhersteller Motorola (heute zu Teilen NXP Semiconductors und ON Semiconductor) entwickeltes Bus-System. Es stellt einen „lockeren“ Standard für einen synchronen seriellen Datenbus (Synchronous Serial Port) dar, mit dem digitale Schaltungen nach dem Master-Slave-Prinzip miteinander verbunden werden können.[1]

Unter der Bezeichnung Microwire gibt es von National Semiconductor ein von SPI abgeleitetes Bus-System.

Grundlagen

[Bearbeiten | Quelltext bearbeiten]Eigenschaften

[Bearbeiten | Quelltext bearbeiten]- Die drei gemeinsamen Leitungen, an die jeder Teilnehmer angeschlossen ist, sind:

- In der Industrie gibt es Bemühungen, die Master/Slave-Terminologie durch neutrale Begriffe zu ersetzen,[2] weshalb in vielen neueren Dokumentationen (z. B. den Arduino-Pinouts) die neueren Namen verwendet werden.

- Manchmal werden die Datenleitungen auch SDO (englisch Serial Data Out) und SDI (englisch Serial Data In) genannt, wobei die Benennung meistens aus der Sicht des jeweiligen Busteilnehmers erfolgt, sodass hier die Leitungen über Kreuz verbunden werden müssen. Statt SDI mit SDI und SDO mit SDO zu verbinden, muss jeweils SDI mit SDO der Gegenstelle verbunden werden.

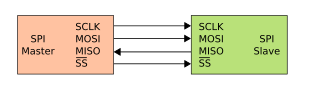

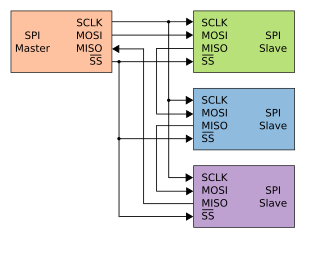

- Eine oder mehrere mit logisch-0 aktive Chip-Select-Leitungen, welche alle vom Controller gesteuert werden und von denen je eine Leitung pro Slave vorgesehen ist. Diese Leitungen werden je nach Anwendung unterschiedlich mit Bezeichnungen wie CS, SS, STE oder CE für Chip Select, Slave Select, Slave Transmit Enable oder Chip Enabler bezeichnet, oft noch in Kombination mit einer Indexnummer zur Unterscheidung. Es gibt auch spezielle Anwendungen, bei denen sich mehrere Chips eine Leitung teilen, siehe Bild 1.

- Vollduplexfähig

- Viele Einstellmöglichkeiten, wie

- mit welcher Taktflanke ausgegeben oder eingelesen wird

- Wortlänge (Anzahl der Bits, die übertragen werden)[3]

- Übertragung: MSB oder LSB zuerst

- Unterschiedliche Taktfrequenzen bis in den MHz-Bereich sind zulässig.

- Vielfältige Einsatzmöglichkeiten in Audio- und Messanwendungen, zur Datenübertragung zwischen Mikrocontrollern.

Viele Einstellungsmöglichkeiten sind unter anderem deshalb erforderlich, weil die Spezifikation für den SPI-Bus in vielen Eigenschaften nicht festgelegt ist, wodurch verschiedene, zueinander inkompatible Geräte existieren. Häufig ist beispielsweise für jeden angeschlossenen Schaltkreis eine eigene Konfiguration des steuernden Mikrocontrollers (Controller des SPI-Bus) erforderlich.

Viele Mikrocontroller, wie die meisten AVR, erlauben über den SPI-Bus eine In-System-Programmierung (kurz auch ISP).

Protokollablauf und Einstellmöglichkeiten

[Bearbeiten | Quelltext bearbeiten]An den Bus können so viele Teilnehmer angeschlossen werden, wie Slave-Select-Leitungen vorhanden sind, zuzüglich des genau einen Masters, der seinerseits das Clock-Signal an SCK erzeugt. Der Master legt mit der Leitung „Slave Select“ fest, mit welchem Slave er kommunizieren will. Wird sie gegen Masse gezogen, ist der jeweilige Slave aktiv und „lauscht“ an MOSI, bzw. legt er seine Daten im Takt von SCLK an MISO. Es wird ein Wort vom Master zum Slave und ein anderes Wort vom Slave zum Master transportiert.

Ein Protokoll für die Datenübertragung wurde von Motorola zwar nicht festgelegt, doch haben sich in der Praxis vier verschiedene „Modi“ durchgesetzt. Diese werden durch die Parameter „Clock Polarity“ (CPOL) und „Clock Phase“ (CPHA) festgelegt. Bei CPOL=0 ist der Clock Idle Low, bei CPOL=1 ist der Clock Idle High. CPHA gibt nun an, bei der wievielten Flanke die Daten übernommen werden sollen. Bei CPHA=0 werden sie bei der ersten Flanke übernommen, nachdem SS auf Low gezogen wurde, bei CPHA=1 bei der zweiten. Somit werden die Daten bei CPOL=0 und CPHA=0 mit der ersten Flanke übernommen, die nur eine steigende Flanke sein kann. Bei CPHA=1 wäre es die zweite, also eine fallende Flanke. Bei CPOL=1 ist es folglich genau andersherum, bei CPHA=0 fallende Flanke und bei CPHA=1 steigende Flanke.

Der Slave legt bei CPHA=0 seine Daten schon beim Herunterziehen von SS an MISO an, damit der Master sie beim ersten Flankenwechsel übernehmen kann. Bei CPHA=1 werden die Daten vom Slave erst beim ersten Flankenwechsel an MISO gelegt, damit sie beim zweiten Flankenwechsel vom Master übernommen werden können. Der Master hingegen legt seine Daten immer zum gleichen Zeitpunkt an, meist kurz nach der fallenden Flanke von SCK.

Mit jeder Taktperiode wird ein Bit übertragen. Beim üblichen Bytetransfer sind also acht Taktperioden für eine vollständige Übertragung nötig. Es können auch mehrere Worte hintereinander übertragen werden, wobei in der Spezifikation nicht festgelegt ist, ob zwischen jedem Wort das SS-Signal kurz wieder auf High gezogen werden muss. Eine Übertragung ist beendet, wenn das Slave-Select-Signal endgültig auf High gesetzt wird.

| Mode | CPOL | CPHA |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

Höhere Datenübertragungsrate mittels Dual und Quad SPI

[Bearbeiten | Quelltext bearbeiten]Um eine höhere Datenübertragungsrate zu erreichen, gibt es unter der Bezeichnung Dual SPI bzw. Quad SPI bei manchen Peripheriebausteinen optional eine parallele Datenübertragung zweier bzw. vierer Bits. Bei Dual SPI erfolgt die Übertragung (mit verdoppelter Datenübertragungsrate) über die beiden Leitungen POCI/MISO und PICO/MOSI in die gleiche Richtung. Somit ist dabei nur Halbduplex-Betrieb möglich; außerdem ist eine umschaltbare Übertragungsrichtung bei den Datenpins notwendig. Bei Quad SPI werden zwei weitere Datenleitungen hinzugenommen, um die Datenübertragungsrate abermals zu verdoppeln. Der SPI-Flash-Baustein W25Q40CL beispielsweise funktioniert dazu zwei Pins um (Hold und Write Protect), deren eigentliche Funktionen dann nicht mehr zur Verfügung stehen.[4]

Varianten

[Bearbeiten | Quelltext bearbeiten]SafeSPI ist ein Industriestandard für SPI in Automobilanwendungen. Sein Hauptaugenmerk liegt auf der Standardisierung der Übertragung von Sensordaten zwischen verschiedenen Geräten.[5]

Weblinks

[Bearbeiten | Quelltext bearbeiten]- SPI – Serial Peripheral Interface ( vom 16. Januar 2019 im Internet Archive), Grundlagenartikel

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Patent US4816996: Queued serial peripheral interface for use in a data processing system. Angemeldet am 24. Juli 1987, veröffentlicht am 28. März 1989, Anmelder: Motorola (heute z. T.: NXP Semiconductors), Erfinder: Susan C. Hill, Joseph Jelemensky, Mark R. Heene.

- ↑ A Resolution to Redefine SPI Signal Names. Abgerufen am 13. Januar 2022 (amerikanisches Englisch).

- ↑ mct.de: SPI - Serial Peripheral Interface. 16. Januar 2019, archiviert vom am 16. Januar 2019; abgerufen am 21. Oktober 2021. Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis.

- ↑ Winbond: 2.5/3/3.3V 4 M-BIT SERIAL FLASH MEMORY WITH 4KB SECTORS, DUAL AND QUAD SPI, Datenblatt für Speicherbaustein W25Q40CL (PDF), Seite 7.

- ↑ FAQ - Frequently Asked Questions. In: SafeSPI. Abgerufen am 29. März 2022.