Tri-State

Als Tri-State werden digitale Schaltungselemente bezeichnet, deren Ausgänge nicht wie üblich nur zwei (0 und 1), sondern zusätzlich noch einen dritten Zustand annehmen können, der mit „Z“ oder auch mit „high impedance“ (hochohmig) bezeichnet wird.

Durch Tri‑States ist es möglich, die Ausgänge mehrerer Bauelemente zusammenzuschalten, ohne dass es zu Kurzschlüssen, einer Überlagerung oder einer Wired-AND- oder Wired-OR‑Verknüpfung kommt, z. B. bei Datenbussen. Verglichen mit den Wired‑And- und Wired‑Or‑Verknüpfungen ist die Tri‑State‑Technik deutlich schneller, da die Tri‑State‑Technik jeweils einen eigenen Schalttransistor zum Umschalten des Ausgangs auf den Low‑Pegel und auf den High‑Pegel besitzt.

Hochohmiger Zustand (Z)

[Bearbeiten | Quelltext bearbeiten]Der hochohmige Zustand (Z) wird von einem Bauelement ausgegeben, wenn dieses keine aktive Eingabe hat. Bei digitalen Schaltungen bedeutet dies, dass das Ausgangssignal weder logisch 0 noch 1 ist, sondern hochohmig. Ein solches Signal sorgt dafür, dass sich das Bauelement verhält, als wäre sein Ausgang temporär von der Schaltung abgetrennt; es beeinflusst also nicht die Ausgaben anderer Bauelemente, die mit diesem parallel geschaltet sind. Es nimmt vielmehr dieselbe Ausgangsspannung wie die momentan aktiven Bauelemente an.

Wahrheitstabelle

[Bearbeiten | Quelltext bearbeiten]

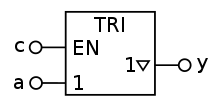

Die nachfolgende Abbildung einer Tri‑State‑Struktur (Funktionsprinzip Tri‑State mit Öffner) stellt einen Schalter in Form eines Öffners dar. Dies entspricht im unbetätigten Zustand (c=0) einem geschlossenen Schalter. Das am Eingang a anliegende Eingangssignal wird in diesem Fall direkt an den Ausgang y weitergeleitet. Wenn am Eingang a ein 0‑Signal anliegt, liegt am Ausgang y ein 0‑Signal an. Das Gleiche gilt jeweils für ein 1‑Signal. Dieser Fall entspricht den beiden ersten Zeilen der Funktionstabelle.

Betrachten wir die zweite Schalterstellung des Schalters c. In diesem Fall liegt an Schalteingang c ein 1‑Signal an. Diese Schalterstellung stellt einen Öffner in betätigter Form dar. Praktisch bedeutet das, dass der Schalter betätigt ist und zwischen dem Eingang a und dem Ausgang y keine elektrische Verbindung vorhanden ist (entspricht dem betätigten Zustand eines Öffners). Schaltungstechnisch entspricht das dem Tri‑State‑Zustand. Im hochohmigen Zustand hat der Ausgang keinen festgelegten Pegel (= hochohmiger Zustand, unbestimmt, abgekürzt Z). In der Funktionstabelle (siehe weiter unten) entspricht dieser Fall der dritten und der vierten Zeile. Unabhängig vom Eingangszustand a liegt am Ausgang der hochohmige Z an.

In der verkürzten Funktionstabelle kann das Tri‑State‑Verhalten auf zwei Zeilen verkürzt werden. Im ersten Fall (erste Zeile) liegt am Ausgang y jeweils der am Eingang a anliegende Logikzustand an. Im zweiten Fall, wenn sich das Gatter im Zustand „Tri‑State“ befindet, liegt am Ausgang y der hochohmige Zustand Z unabhängig vom Eingangszustand a an. Dieses Verhalten wird als Low‑aktive Ansteuerung der Tri‑State‑Schaltung bezeichnet.

|

|

|

Technischer Einsatz der Tri-State-Technik

[Bearbeiten | Quelltext bearbeiten]

Die Anzahl der parallel geschalteten Tri‑State-Bauelemente ist begrenzt. Jeder Tri‑State‑Ausgang besitzt geringe Leckströme, die sich bei der Parallelschaltung der Tri‑State-Bauelemente addieren und somit die Signalpegel mit verzerren können.

Weiterhin ist zu berücksichtigen, dass die Ausgänge der Tri‑State-Bauelemente alle miteinander verbunden werden müssen. Diese Verbindungsleitungen besitzen parasitäre Kondensatoren, die bei jedem Schaltvorgang von High nach Low und von Low nach High jeweils umgeladen werden müssen. Weiterhin besitzen die Verbindungsleitungen einen ohmschen Widerstand. Je größer die Anzahl von parallel geschalteten Bauelementen ist, desto größer ist der Kapazitätswert. Dadurch steigt auch der Widerstandswert und folglich auch die Signalbeeinflussung. Beispielsweise nimmt dadurch die Flankensteilheit des Ausgangssignals bei den Schaltvorgängen ab. Als Folge nimmt die maximal erreichbare Taktfrequenz mit der Anzahl der parallel geschalteten Bauelemente ab.

Da an Tri‑State‑Ausgängen meist auch Eingänge von Logikbausteinen angeschlossen sind, muss ein definierter Logikzustand anliegen. Das bedeutet, dass immer ein Bauteil ein aktives Low- oder High‑Signal senden muss – mindestens ein Ausgang darf sich nicht im Tri‑State‑Zustand befinden. Als Alternative kann ein Pull‑Up-Widerstand (zwischen Ausgang und der Versorgungsspannung) oder ein Pull‑Down‑Widerstand (zwischen Ausgang und Masse) verwendet werden. Dieser sorgt dann für einen definierten Signalpegel, wenn kein Tri‑State‑Treiber aktiv ist.

Bei programmierbaren logischen Schaltungen (PLD) oder FPGA-Bauelementen kann die Tri‑State‑Technik ebenfalls verwendet werden, hier jedoch ausschließlich an den Bauelementanschlüssen nach außen hin. Innerhalb der Bauelemente kommen zum Umschalten ausschließlich Multiplexer zum Einsatz. Das Gleiche gilt für Anwendungsspezifische integrierte Schaltungen (ASICs).

Weblinks

[Bearbeiten | Quelltext bearbeiten]Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Praktische Realisierung logischer Schaltungen ( des vom 11. Oktober 2007 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis., Rechenzentrum Elektrotechnik der Fachhochschule Kiel, 9. Oktober 2012