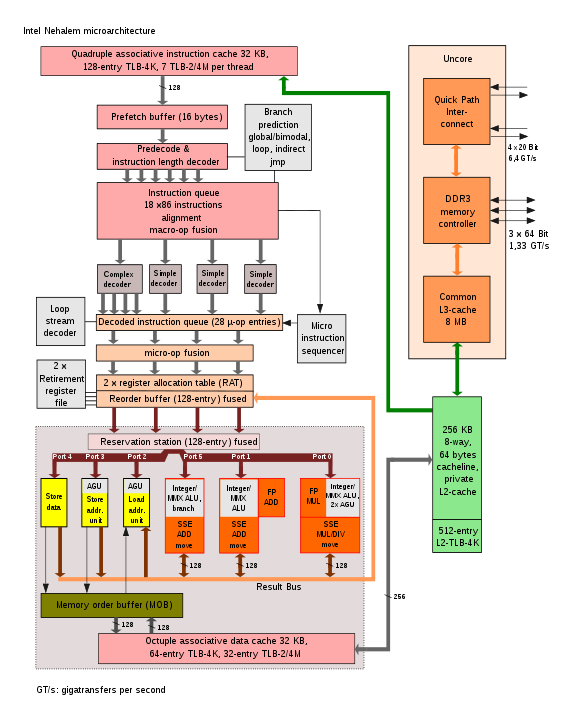

Intel-Nehalem-Mikroarchitektur

| Nehalem (Mikroarchitektur) | |

|---|---|

| Hersteller | Intel |

| Herstellungsprozess | 45 nm (Nehalem) 32 nm (Westmere) |

| Sockel | Sockel 1156 (2 Speicherkanäle) Sockel 1366 (3 Speicherkanäle) |

| L1-Cache | 32+32 kB pro Kern |

| L2-Cache | 256 kB pro Kern |

| L3-Cache | 3/4/6/8/12 MB |

| Vorgänger | Intel Core Solo (Yonah) Intel Core Duo (Yonah) Intel Core 2 (Allendale, Conroe, Merom, Kentsfield, Penryn, Wolfdale, Yorkfield) |

| Nachfolger | Sandy Bridge (tock) Ivy Bridge (tick) |

Die Intel-Nehalem-Mikroarchitektur ist eine von Intel entwickelte Mikroarchitektur. Sie basiert teilweise auf der Intel-Core-Mikroarchitektur und löste diese im Jahr 2008 ab. Prozessoren auf Basis der Nehalem-Architektur sind die ersten Intel-Prozessoren mit integriertem Speichercontroller. Die erste Version der Nehalem-Architektur ist als High-End-CPU (Bloomfield) für Desktop-PCs als Core i7 für den Sockel 1366 (X58) im November 2008 auf den Markt gekommen.

Sie wurde 2011 durch die Intel-Sandy-Bridge-Mikroarchitektur ersetzt.

Der Name dieser Mikroarchitektur geht auf eine kleine Küstenstadt namens Nehalem an der Mündung des Nehalem Rivers in Oregon zurück.[1][2]

Neuerungen der Nehalem-Architektur

[Bearbeiten | Quelltext bearbeiten]Eine Hauptneuerung dieser Architektur ist, dass der Front Side Bus (FSB), der bei Vorgängern die Verbindung zwischen Prozessor und Chipsatz herstellte, einer Punkt-zu-Punkt-Verbindung namens QuickPath Interconnect (QPI) gewichen ist, die auf hohen Durchsatz und Skalierbarkeit ausgelegt ist – ähnlich dem Umstieg AMDs auf HyperTransport fünf Jahre vorher. Eine weitere wichtige Neuerung, ebenfalls ähnlich wie bei AMD, ist die Anbindung des Arbeitsspeichers über einen integrierten Speichercontroller. Durch diese direkte Verbindung kann der Prozessor mit deutlich geringerer Latenz auf den Speicher zugreifen. Diese beiden Maßnahmen schaffen den bis dato vorhandenen Flaschenhals der Core-Prozessoren ab, der durch den FSB gegeben war. Allerdings sind dadurch neue Sockel nötig.

Es wird zusätzlich Simultaneous Multithreading (SMT) implementiert, welches bereits in Pentium-4-Prozessoren unter dem Namen Hyper-Threading zum Einsatz kam. Die neue Umsetzung generiert deutlich mehr Leistung, auch weil die Ressourcen pro Thread durch das vierfach superskalare Design im Gegensatz zum dreifach superskalaren Design des Pentium 4 gestiegen sind. Mit Intels SMT kann der Prozessor mit vier Kernen maximal acht Threads gleichzeitig abarbeiten.[3] Der Nutzen bei einem Vierkerner war bei Desktopanwendungen jedoch fraglich, da nur bei speziell hierauf optimierter Software derart viele leistungsrelevante Threads zugleich ablaufen. Bisher leiden auch „normale“ Quadcores daran, von den wenigsten Programmen ausgenutzt zu werden und daher, bedingt durch einen geringeren Takt pro Kern, in den Anwendungen teilweise langsamer als Dualcore-Modelle zu sein. Im Server-Bereich machen sich dagegen mehrere – reale oder virtuelle – Prozessoren tendenziell eher nützlich, da häufiger eine Anzahl von Requests parallel zu verarbeiten ist.

Gegenüber seinen Vorgängern weist die Nehalem-Architektur eine dreistufige Cache-Hierarchie ähnlich der des AMD Phenom auf: Jeder Kern besitzt neben einem eigenen L1-Cache auch einen eigenen 256 KiB großen L2-Cache, während sich alle Kerne einen gemeinsamen L3-Cache teilen, der bis zu 8 MiB groß ist. Dies ist effektiv weniger als die zuletzt bis zu 6 MiB für je zwei Kerne beim Core 2, jedoch ist der Nutzen derart großer Caches fraglich; in diesem Punkt abgespeckte Versionen des Core 2 verloren oft nur minimal an Leistung. Letzterer ist ein Inklusivcache, d. h., er beinhaltet stets auch alle Daten, die in L1- oder L2-Caches abgelegt sind. Damit wird das Cachekohärenzprotokoll vereinfacht und Snooping-Traffic verringert. Die L1- und L2-Caches bestehen im Gegensatz zu den Vorgängerprozessoren nicht mehr aus gewöhnlichen 6T-SRAM-, sondern aus 8T-SRAM-Zellen, wodurch sich Intel Ersparnisse beim Energiebedarf erhofft.[4]

Die Power Control Unit (PCU), eine Art Koprozessor für die Energieverwaltung des Prozessors, und neuartige Leistungsgatterschaltungen sollen für eine Optimierung des Energiehaushaltes sorgen.[5] Dadurch soll zum einen die Leistungsaufnahme in jeder Lastsituation minimal gehalten werden, andererseits wird damit der sogenannte Turbo Mode[6] implementiert, bei dem der Prozessor bei entsprechender schwach auf Threads verteilter Last automatisch etwas höher getaktet wird, wenn es der Energiehaushalt des Prozessors zulässt. Konkret heißt das: Wenn zwei physische Kerne unbenutzt sind und die TDP nicht überschritten wird, werden die in Benutzung befindlichen Kerne um mindestens eine Multiplikatorstufe höher getaktet. Arbeitet gar nur ein Kern, fällt die Taktfrequenzsteigerung des arbeitenden Kerns noch größer aus. Die inaktiven Kerne werden heruntergetaktet.[7]

Zu den weiteren Neuerungen gehört eine weitere Ausbaustufe der Streaming SIMD Extensions, SSE4.2, und dass alle vier Prozessorkerne auf demselben Die untergebracht sind.

Bloomfield

[Bearbeiten | Quelltext bearbeiten]

Als erster Intel-Prozessor für den Desktopmarkt hat der Bloomfield den Speichercontroller direkt auf dem Chip integriert, wie es AMD schon seit den Prozessoren auf Basis der K8-Architektur praktiziert. Der Prozessor verfügt über drei Speicherkanäle, durch die ähnlich dem bisher üblichen Dual-Channel-Modus je drei identische Speichermodule parallel genutzt werden können; es ist jedoch auch möglich, nur zwei der Kanäle zu verwenden. Als Speichertyp kommt ausschließlich DDR3-RAM mit offiziell bis zu 1333 MHz Takt (DDR3-1066) zum Einsatz; ein alternativer Einsatz von DDR2-RAM ist nicht mehr möglich. Die Kommunikation zur Northbridge erfolgt durch den sogenannten QuickPath Interconnect (QPI), welcher je nach Modell mit 9,6–12,8 GB/s[8] in jede Richtung eine sehr breitbandige Punkt-zu-Punkt-Verbindung darstellt, ähnlich dem von AMD genutzten HyperTransport. QPI löst damit den in seiner Grundform noch aus Urzeiten der x86-Familie stammenden Front Side Bus ab. Alle Prozessoren mit dem Bloomfield-Kern beherrschen die sogenannte Turbo-Boost-Technik: Im Fall der Auslastung eines einzelnen Kerns wird der Multiplikator dieses Kerns um zwei Zählerpunkte erhöht, während andere Kerne heruntergetaktet werden, im Falle der Auslastung von zwei bis vier Kernen werden deren Multiplikatoren um maximal einen Zählerpunkt erhöht, sofern die Auslastung der Kerne nicht die maximale TDP des Prozessors ohne diese Takterhöhung fordert.[9]

- Chipsatz für bloomfieldbasierte Prozessoren

Aufgrund der Leistungseinstufung stellt Intel als Chipsatz nur eine teure Variante zur Verfügung, die „Intel X58“ getauft wurde. Der unter dem Codenamen Tylersburg entwickelte Chipsatz verfügt – im Gegensatz zu späteren, günstigeren Prozessorserien auf Basis der Nehalem-Architektur – noch über eine klassische Bauweise aus North- und Southbridge.

Chipsätze anderer Hersteller gibt es nicht für Bloomfield-Prozessoren. Nvidia hatte in einer Pressemitteilung angekündigt, dass die SLI-Fähigkeit für Plattformen mit dem Core-i7-Prozessoren über einen Zusatzchip an den X58 realisiert wird.[10] Letzten Endes konnten Intel und Nvidia sich aber darauf einigen, dass Nvidia ähnlich wie ATI eine Lizenz für das Integrieren der Multi-GPU-Technik in die X58-Chipsätze anbietet.

- Fehlerverzeichnis der Bloomfield-basierten Prozessoren

Intel beschreibt in seinem „Specification Update“ vom 12. November 2008 für den Core i7[11] ein Erratum bezüglich des Translation Lookaside Buffers, das bereits in früheren Prozessorserien von Intel und AMD auftrat.[12] Bereits vor der Markteinführung wurden aber die Mainboardhersteller von Intel aufgefordert, den Fehler durch ein BIOS-Update zu umgehen. Intel geht davon aus, dass die Hersteller dieser Aufforderung auch nachgekommen sind.[13]

Lynnfield

[Bearbeiten | Quelltext bearbeiten]

Lynnfield ist ein in 45 nm Strukturgröße gefertigter Quad-Core-Prozessor, der mittels Simultaneous Multithreading (bei einigen Modellen deaktiviert) bis zu acht Threads gleichzeitig ausführen kann. Wie beim Bloomfield sitzt der Speichercontroller auf dem Prozessor-Die. Im Gegensatz zu diesem spricht der Speichercontroller von Lynnfield den DDR3-Speicher im Dual-Channel-Verfahren an.[14] Ebenfalls aus der Bloomfield-Serie stammt die integrierte Turbo-Boost-Technik, die je nach Auslastung der einzelnen Kerne deren Taktfrequenzen unterschiedlich erhöht, ohne dabei die TDP zu überschreiten; die maximale Takterhöhung fällt aber stärker aus, als dies beim Bloomfield der Fall ist. Im Fall der Auslastung eines einzelnen Kerns wird der Multiplikator dieses Kerns um fünf Zählerpunkte, im Falle der Auslastung von zwei Kernen um vier Zählerpunkte erhöht, während inaktive Kerne heruntergetaktet werden, im Falle der Auslastung von drei bis vier Kernen werden deren Multiplikatoren um maximal einen Zählerpunkt erhöht, sofern die Auslastung der Kerne nicht die maximale TDP des Prozessors ohne diese Takterhöhung fordert. Der Lynnfield hat außerdem die Stromsparfunktion EIST, die Taktrate und Betriebsspannung des Prozessors bei Nichtauslastung absenkt.

Im Gegensatz zum Bloomfield wurde nicht nur der Speichercontroller, sondern die gesamte Northbridge samt PCI-Express-Controller in den Prozessor integriert, die Kommunikation erfolgt dort weiterhin (nun aber prozessorintern) über den QuickPath Interconnect. Auf der Hauptplatine ist dementsprechend nur noch eine Southbridge verbaut, die wie bei Intel üblich über ein Direct Media Interface (DMI) angebunden wird. Alle Lynnfield-CPUs können mit Chipsätzen der Intel-5-Serie eingesetzt werden. Da der Prozessor aber den Sockel 1156 nutzt, kann er nicht auf den für den Bloomfield gedachten X58-Mainboards betrieben werden.

Auf die Fertigstellung des Dual-Core-Ablegers Havendale verzichtete Intel frühzeitig zu Gunsten von Clarkdale.[15]

Clarksfield

[Bearbeiten | Quelltext bearbeiten]Clarksfield ist im Kerndesign identisch zum Lynnfield. Der CPU-Die wird jedoch in ein Chipgehäuse für den Sockel 988 gepackt. Zudem werden alle Prozessoren mit einer niedrigen TDP verkauft, da sie für das mobile Marktsegment bestimmt sind. Der maximal mögliche Takt eines Kerns im Turbomodus fällt im Verhältnis zum Standardtakt noch einmal höher aus, als dies bei den Desktopmodellen auf Lynnfield-Basis der Fall ist. Letzten Endes hängt aber die Ausnutzung dieses Taktspielraums ganz entscheidend von der Kühlung ab, da sich die Turbo-Boost-Technologie auch an der Temperatur orientiert.

Westmere

[Bearbeiten | Quelltext bearbeiten]Unter dem Namen „Westmere“ (ursprünglich: Nehalem-C) wurden im Januar 2010 die ersten auf der Nehalem-Mikroarchitektur basierenden aber auf 32 nm Strukturgröße geschrumpften Prozessoren eingeführt. Die ersten Chips dieser Art waren die Dual-Core-Prozessoren der Bezeichnung Clarkdale. Im Gegensatz zu den Vierkernern der Nehalem-Architektur entfällt bei diesen Prozessoren wieder der auf dem CPU-Die integrierte Speichercontroller. Stattdessen wird dieser im CPU-Gehäuse, aber auf einem anderen Chip untergebracht. Die Kommunikation erfolgt aber nicht wieder über FSB, sondern über QPI, was aber nicht zu besseren Latenzen bei Speicherzugriffen im Vergleich zur FSB-Anbindung führt.[16] Einen Geschwindigkeitsvorteil gegenüber den Dual-Cores auf der Core-Architektur erfahren die neuen Westmere-Dual-Cores lediglich durch Simultaneous Multithreading (SMT). Mit deaktiviertem SMT ist die Leistung pro Takt daher ähnlich der älteren Core-Architektur.[17] Mit SMT verhalten sich die neuen Dual-Cores mit vierfach superskalaren Kerndesign ähnlich wie die Tricore-Modelle mit dreifach superskalaren Kerndesign bei Benchmarks mit unterschiedlich stark in Threads aufgeteilter Software.

Im ersten Halbjahr 2010 wurden auch Sechskerner und Vierkerner auf Basis des Gulftowns vorgestellt. Diese Westmere-CPUs unterscheiden sich in der Architektur nicht von Bloomfield-CPUs, lediglich die Fertigung wurde auf den 32-nm-Prozess umgestellt. Somit sind zusätzliche Kerne und mehr Cache innerhalb gleicher TDP-Grenzen möglich. Außerdem wurden, wie schon bei den Dual-Core-Westmere-CPUs, sieben zusätzliche Instruktionen hinzugefügt, wovon sechs der AES-Verschlüsselung dienen: Es sind dies AES-NI und CLMUL. Der größere L3-Cache hat zudem etwas größere Latenzen als der Vorgänger.[18]

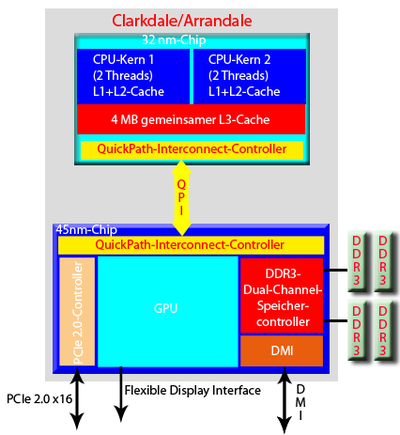

Clarkdale

[Bearbeiten | Quelltext bearbeiten]

Die CPU-Kerne des Clarkdale entsprechen technisch weitestgehend denen vom Lynnfield, sind aber in 32-nm-Verfahren gefertigt. Im Gegensatz zum Lynnfield besitzt der Clarkdale nur zwei Kerne und der Speichercontroller ist nicht direkt mit den Kernen verbunden, sondern befindet sich auf dem gleichen Die mit dem GPU-Kern und wird über den QPI angebunden, was im Vergleich zu Lynnfield zu deutlich höheren Latenzen bei Speicherzugriffen seitens des Prozessors führt.[19] Der Halbleiter-Chip mit dem GPU-Kern und dem Speichercontroller wird im 45-nm-Verfahren gefertigt und bei allen Clarkdale-Prozessoren im gleichen Chip-Package wie die CPU untergebracht.

Wegen der Verkleinerung der Strukturgröße ordnet Intel die Clarkdale-Prozessoren einer neuen Prozessorgeneration mit dem Codenamen „Westmere“ zu. Im Rahmen der Westmere-Architektur hat der Clarkdale sieben neue Instruktionen (bei einigen Modellen deaktiviert), von denen sechs der AES-Verschlüsselung gewidmet sind.[20]

Wie Lynnfield werden die Clarkdale-Prozessoren im Sockel 1156 betrieben und können auf Chipsätzen der Intel-5-Serie eingesetzt werden. Die integrierte Grafikeinheit kann jedoch nicht auf Mainboards mit dem P55-Chipsatz genutzt werden, sondern nur mit den neueren Chipsätzen (H55, H57, Q57). Die Bildsignale von der integrierten GPU werden dabei über das „Flexible Display Interface“ (FDI) zum Chipsatz übertragen, wobei FDI auf dem DisplayPort-Standard basiert.[21]

Arrandale

[Bearbeiten | Quelltext bearbeiten]Arrandale entspricht technisch gesehen dem Clarkdale, ist aber für den Einsatz in Notebooks optimiert. Deshalb ist er für den Betrieb in Sockeln PGA988 und BGA1288 vorgesehen und hat eine gesenkte TDP, welche teilweise mit reduzierten Taktraten und reduzierter Spannung erreicht wird. Ab den Arrandale-Prozessoren wurden die Notebooks zudem WiDi-fähig (Intel Wireless Display), insofern auch ein WLAN-Adapter aus der Centrino-Serie vorhanden ist.

Gulftown

[Bearbeiten | Quelltext bearbeiten]Am 11. März 2010 erschienen die ersten Core-i7-Prozessoren mit Gulftown-Architektur.[22] Das erste Modell war der i7-980X Extreme Edition mit einer Taktfrequenz von 3,33 GHz. Bei den Prozessoren mit Gulftown-Architektur handelt es sich um die ersten nativen Sechskernprozessoren (Hexa-Core) von Intel. Da dieser im 32-nm-Fertigungsprozess hergestellt wird, ordnet ihn Intel, genau wie den Clarkdale, der Westmere-Generation zu. Der Gulftown setzt leistungsmäßig oberhalb des Bloomfield an, wird für den Sockel 1366 hergestellt und kann mit dem X58-Chipsatz betrieben werden. Gulftown unterstützt Hyper-Threading und bringt außerdem spezielle Funktionen zur beschleunigten Verschlüsselung in Form der AES New Instructions (AES-NI) mit.

Modelle

[Bearbeiten | Quelltext bearbeiten]Desktop

[Bearbeiten | Quelltext bearbeiten]Clarkdale

[Bearbeiten | Quelltext bearbeiten]- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 4096 KiB mit QPI-Takt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, SMT. Nur bei Core i5-Modellen freigeschaltet: AES-Instruktionen, TXT. Ausnahme: Core i5-661 ohne TXT und Intel VT-d![23]

- über QPI angebundener Dual-Channel-DDR3-Speichercontroller, PCIe 2.0-Controller und GPU

- Sockel 1156, Direct Media Interface (DMI) und Flexible Display Interface (FDI)

- Betriebsspannung (VCore): 0,65–1,4 V

- Verlustleistung (TDP): 73–87 W

- Erscheinungsdatum: 4. Januar 2010

- Fertigungstechnik: 32 nm (45 nm beim GPU-Kern mit Speichercontroller und PCIe-Controller)

- Die-Größe: 81 mm² bei 383 Millionen Transistoren sowie 114 mm² bei 177 Millionen Transistoren für den GPU-Kern[24]

- Taktraten: 2,8–3,6 GHz

- Modelle: Intel Core i3-530 bis Intel Core i5-680

Lynnfield

[Bearbeiten | Quelltext bearbeiten]- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 8192 KiB mit QPI-Takt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT. Nur bei Core i7 freigeschaltet: SMT, TXT

- integrierter Dual-Channel-DDR3-Speichercontroller; über internen QPI mit 2,13–2,4 GHz (17,07–19,2 GB/s) angebundener PCIe-2.0-Controller mit 16 Lanes

- Sockel 1156, DMI mit 2,5 GT/s (Vollduplex, max. 10 Gb/s pro Richtung,[25] insgesamt 2 GB/s)

- Betriebsspannung (VCore): 0,65–1,4 V

- Verlustleistung (TDP): 82–95 W

- Erscheinungsdatum: 8. September 2009

- Fertigungstechnik: 45 nm

- Die-Größe: 296 mm² bei 774 Millionen Transistoren[26]

- Taktraten: 2,66–3,06 GHz

- Modelle: Intel Core i5-750 bis Intel Core i7-880

Bloomfield

[Bearbeiten | Quelltext bearbeiten]- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 8192 KiB mit QPI-Takt

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, SMT

- integrierter Triple-Channel-DDR3-Speichercontroller: Unterstützung bis zu DDR3-1066

- Sockel 1366, QuickPath Interconnect mit 2,4–3,2 GHz (9,6–12,8 GB/s in jede Richtung, bzw. 19,2–25,6 GB/s insgesamt)

- Betriebsspannung (VCore): 0,8–1,375 V

- Verlustleistung (TDP): 130 W

- Erscheinungsdatum: 18. November 2008[27]

- Fertigungstechnik: 45 nm

- Die-Größe: 263 mm² bei 731 Millionen Transistoren[26]

- Taktraten: 2,66–3,33 GHz

- Modelle: Intel Core i7-920 bis Intel Core i7-975 Extreme Edition

Gulftown

[Bearbeiten | Quelltext bearbeiten]

Sechskernprozessor (Hexa-Core)

- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 12 MiB

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, SMT, TXT, AES-Instruktionen

- integrierter Triple-Channel-DDR3-Speichercontroller: Unterstützung bis zu DDR3-1066

- Sockel 1366, QuickPath Interconnect mit 3,2 GHz (12,8 GB/s in jede Richtung, bzw. 25,6 GB/s insgesamt)

- Betriebsspannung (VCore): 0,8–1,375 V

- Verlustleistung (TDP): 130 W

- Erscheinungsdatum: 16. März 2010

- Fertigungstechnik: 32 nm

- Die-Größe: 248 mm² bei 1,17 Milliarden Transistoren

- Taktraten: 3,20–3,46 GHz

- Modelle: Intel Core i7-970 bis Intel Core i7-990X Extreme Edition

Mobil

[Bearbeiten | Quelltext bearbeiten]Clarksfield

[Bearbeiten | Quelltext bearbeiten]- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 6144-8192 MiB, bei einigen Modellen Teil-deaktiviert

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, SMT, TXT

- integrierter Dual-Channel-DDR3-Speichercontroller; über internen QPI angebundener PCIe-2.0-Controller

- Sockel PGA988, DMI mit 2,5 GT/s (Vollduplex, max. 10 Gbit/s pro Richtung,[25] insgesamt 2 GB/s)

- Betriebsspannung (VCore): 0,65–1,4 V

- Verlustleistung (TDP): 45–55 W

- Erscheinungsdatum: 23. September 2009

- Fertigungstechnik: 45 nm

- Die-Größe: 296 mm² bei 774 Millionen Transistoren

- Taktraten: 1,6–2,13 GHz

- Modelle: Intel Core i7-720QM bis i7-940XM Extreme Edition

Arrandale

[Bearbeiten | Quelltext bearbeiten]- L1-Cache: je Kern 32 + 32 KiB (Daten + Instruktionen)

- L2-Cache: je Kern 256 KiB mit Prozessortakt

- L3-Cache: 4096 KiB (bei einigen Modellen nicht komplett freigeschaltet)

- MMX, SSE, SSE2, SSE3, SSSE3, SSE4.2, Intel 64, EIST, XD-Bit, IVT, SMT. Ab Core i5-520M auch AES-Instruktionen und TXT freigeschaltet.

- über QPI angebundener Dual-Channel-DDR3-Speichercontroller, PCIe-2.0-Controller und GPU

- Sockel PGA988, Direct Media Interface (DMI) und Flexible Display Interface (FDI)

- Sockel BGA1288, Direct Media Interface (DMI) und Flexible Display Interface (FDI)

- Betriebsspannung (VCore): k. A.

- Verlustleistung (TDP): 18–37 W

- Erscheinungsdatum: 4. Januar 2010

- Fertigungstechnik: 32 nm (45 nm beim GPU-Kern mit Speichercontroller und PCIe-Controller)

- Die-Größe: 81 mm² bei 383 Millionen Transistoren für die CPU, sowie zusätzlich 114 mm² bei 177 Millionen Transistoren für den Uncore-Bereich[24]

- Taktraten: 1,06–2,80 GHz

- Modelle: Intel Core i3-330M bis Intel Core i7-640M

Siehe auch

[Bearbeiten | Quelltext bearbeiten]Weblinks

[Bearbeiten | Quelltext bearbeiten]- Nehalem – Everything You Need to Know about Intel’s New Architecture – Artikel bei Anandtech (englisch)

Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ King Ian: Intel’s new faster chip right on AMD’s heels. The Seattle Times, 20. Oktober 2008, abgerufen am 21. Januar 2011.

- ↑ George Jones: IAMD vs Intel: The future of desktop CPUs. PC Advisor UK, 9. Februar 2008, abgerufen am 21. Januar 2011.

- ↑ Allround-PC.com: Intel Core i7 – Die Details kurz vor der Markteinführung ( des vom 26. Januar 2009 im Internet Archive) Info: Der Archivlink wurde automatisch eingesetzt und noch nicht geprüft. Bitte prüfe Original- und Archivlink gemäß Anleitung und entferne dann diesen Hinweis., Nachricht vom 4. November 2008

- ↑ Nehalem – Everything You Need to Know about Intel’s New Architecture. AnandTech. S. 9 (Artikel über die Nehalem-Architektur).

- ↑ Nehalem – Everything You Need to Know about Intel’s New Architecture. AnandTech. S. 12 (Artikel über die Nehalem-Architektur).

- ↑ Andreas Stiller: IDF: Nehalem mit Turbo-Modus Heise online. 20. August 2008.

- ↑ Christof Windeck: Intel Core i7 jetzt im Handel. Heise online. 17. November 2008.

- ↑ Nehalem – Everything You Need to Know about Intel’s New Architecture. In: AnandTech, Artikel über die Nehalem-Architektur, Seite 11, Abschnitt „QPI“

- ↑ Increasing Performance with Intel® Turbo Boost Technology ( vom 3. Januar 2013 im Webarchiv archive.today) Intel, abgerufen am 26. März 2009

- ↑ NVIDIA Brings SLI Technology to Intel Bloomfield CPU Platforms. Nvidia Corporation, Pressemitteilung vom 14. Juli 2008 (englisch)

- ↑ Intel Core i7 Processor Extreme Edition Series and Intel Core i7 Processor Specification Update. Intel (PDF; 786 kB)

- ↑ Auch Intels Core-i7-Prozessoren brauchen bei der TLB Invalidation Aufmerksamkeit. In: heise online, 1. Dezember 2008

- ↑ TLB-Bug im Intel Core i7! – Oder doch nicht? In: ComputerBase, 1. Dezember 2008

- ↑ Erste Benchmarks des Core i5 „Lynnfield“. In: ComputerBase, 9. Dezember 2008

- ↑ (Fast) offiziell: Clarkdale ersetzt Havendale. In: ComputerBase, 9. Februar 2009

- ↑ AnandTech: The Clarkdale Review: Intel’s Core i5 661, i3 540 & i3 530, Testbericht vom 4. Januar 2010.

- ↑ ComputerBase: Test: Intel Core i3-530/540 und Core i5-661, Testbericht vom 4. Januar 2010.

- ↑ AnandTech: A 12 MB L3 Cache: 50 % Larger, 14 % Higher Latency, Testbericht vom 11. März 2010.

- ↑ The Clarkdale Review: Intel’s Core i5 661, i3 540 & i3 530. In: AnandTech, 4. Januar 2010.

- ↑ Test: Intel Core i3-530/540 und Core i5-661 (Seite 6). In: ComputerBase, 4. Januar 2010.

- ↑ Intel Core i5-600 und Core i3-500 Serie sowie Pentium G6950 ( vom 6. Februar 2016 im Internet Archive) Intel, Datenblatt PDF.

- ↑ Sechs-Kern-Prozessor von Intel. In: heise online, 11. März 2010

- ↑ Intel Prozessor Spezifikation Core i5 661. Intel, 22. Januar 2010.

- ↑ a b Test: Intel Core i3-530/540 und Core i5-661 (Seite 3). In: ComputerBase, 4. Januar 2010, abgerufen am 4. Januar 2010.

- ↑ a b Intel 5 Series Chipset and Intel 3400 Series Chipset ( vom 26. April 2015 im Internet Archive). Intel, Datenblatt, September 2009, abgerufen am 1. Januar 2010.

- ↑ a b Test: Intel Core i5-750, Core i7-860 und Core i7-870 – Der Lynnfield-Prozessor. In: ComputerBase, 8. September 2009, abgerufen am 1. Januar 2010.

- ↑ Intel präsentiert den schnellsten Prozessor aller Zeiten ( vom 25. Dezember 2008 im Internet Archive) Intel, Pressemitteilung vom 18. November 2008